#### The McGraw·Hill Companies

#### **CMOS Digital Integrated Circuits**

#### Chapter 10 Semiconductor Memories

S.M. Kang, Y. Leblebici, and C. Kim

Copyright © 2014 McGraw-Hill Education. Permission required for reproduction or display.

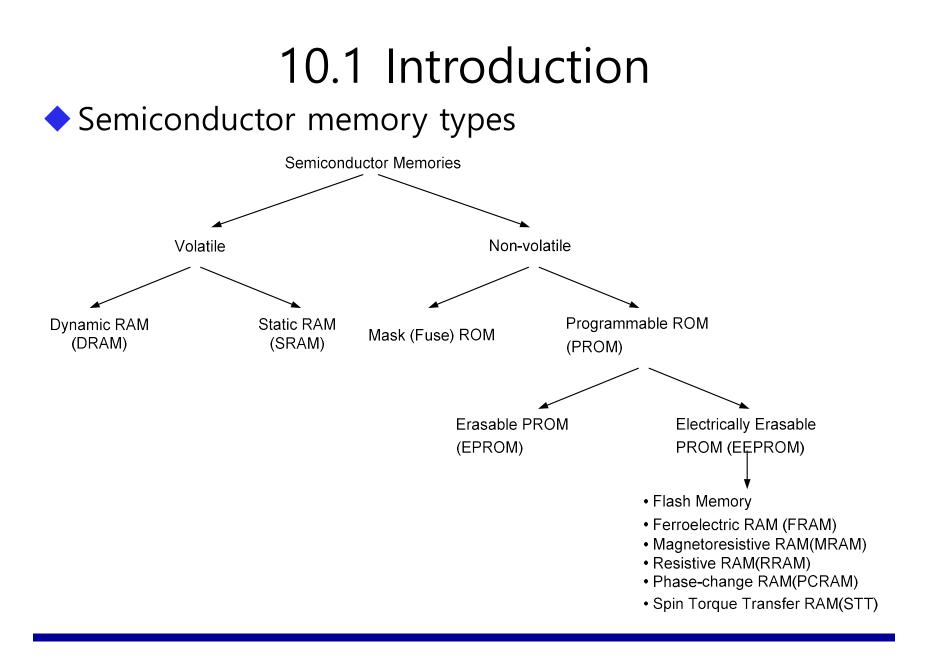

### 10.1 Introduction

#### Design issue

- Area efficiency -> cost per bit

- Access time -> speed

- Power consumption -> low-power

| Characteristic Summary of Memory Devices             |                |            |                  |          |                                    |                                  |

|------------------------------------------------------|----------------|------------|------------------|----------|------------------------------------|----------------------------------|

|                                                      | Memory type    |            |                  |          |                                    |                                  |

|                                                      | DRAM           | SRAM       | UV EPROM         | EEPROM   | Flash                              | FRAM                             |

| Data volatility                                      | Yes            | Yes        | No               | No       | No                                 | No                               |

| Data refresh operation                               | Required       | No         | No               | No       | No                                 | No                               |

| Cell structure                                       | 1T-1C          | 6Т         | 1T               | 2T       | 1T                                 | 1T-1C                            |

| Cell size(F <sup>2</sup> )<br>(F: min. feature size) | 6~8            | 80~100     |                  |          | 4~5(NAND)<br>9~10(NOR)             |                                  |

| Cell density                                         | High           | Low        | High             | Low      | High                               | High                             |

| Power consumption                                    | High           | High/low   | Low              | Low      | Low                                | High                             |

| Read speed (latency)                                 | ~50 ns         | ~10/70 ns  | ~50 ns           | ~50 ns   | ~50 ns                             | ~100 ns                          |

| Write speed                                          | ~40 ns         | ~5/40 ns   | ~10 µs           | ~5 ms    | ~(10 µs-1 ms)                      | ~100 ns                          |

| Endurance                                            | High           | High       | High             | Low      | High                               | High                             |

| Cost                                                 | Low            | High       | Low              | High     | Low                                | Low                              |

| In-system writability                                | Yes            | Yes        | No               | Yes      | Yes                                | Yes                              |

| Power supply                                         | Single         | Single     | Single           | Multiple | Single                             | Single                           |

| Application example                                  | Main<br>memory | Cache/PDAs | Game<br>machines | ID card  | Memory card<br>solid-state<br>disk | Smart card,<br>digital<br>camera |

#### Characteristic Summary of Memory Devices

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

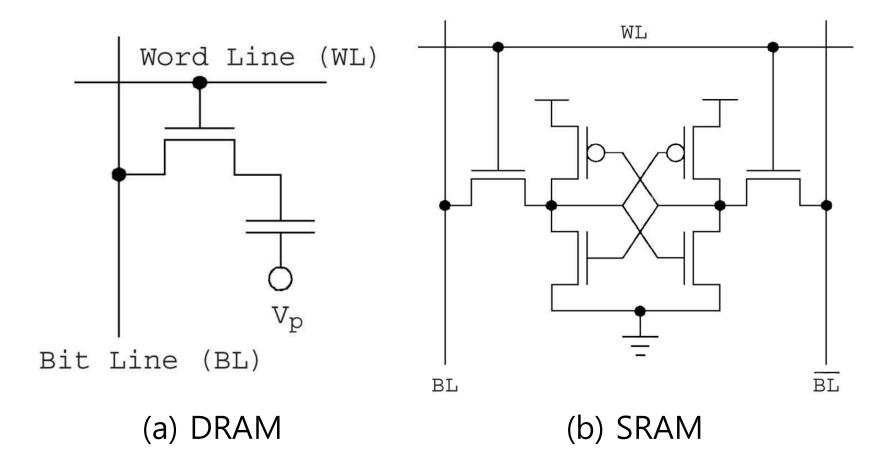

## Equivalent Circuits of Memory Cells(1)

## Equivalent Circuits of Memory Cells(2)

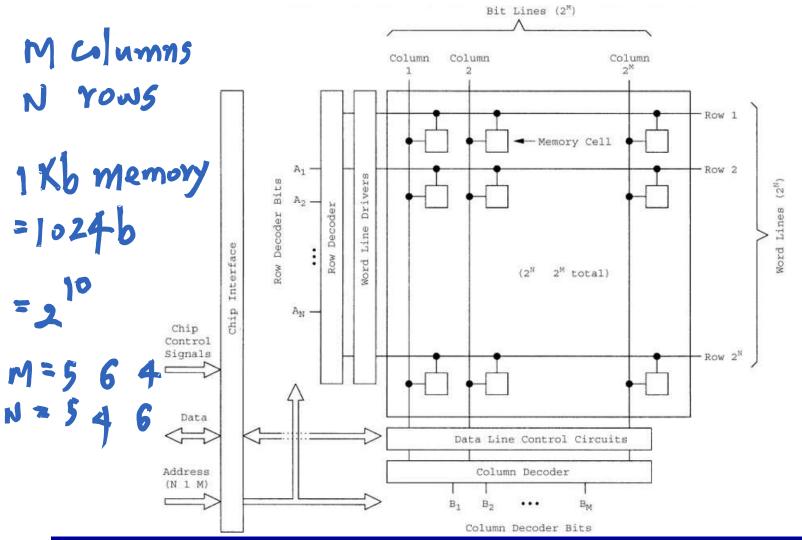

# Conceptual RAM Array Organization

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

## 10.2 Dynamic Random Access Memory

| DQ PAD                                                             |  |  |  |  |  |

|--------------------------------------------------------------------|--|--|--|--|--|

| CELLARRAY<br>ROWDEC ROWDEC CELLARRAY CELLARRAY CELLARRAY CELLARRAY |  |  |  |  |  |

|                                                                    |  |  |  |  |  |

| ROWDEC                                                             |  |  |  |  |  |

|                                                                    |  |  |  |  |  |

| Typical configuration of DRAM chip                                 |  |  |  |  |  |

| (1.6Gbps 4Gb 30nm LPDDR3 w/ 8 banks)                               |  |  |  |  |  |

| chip size 🔶 performance                                            |  |  |  |  |  |

| The number of cells per word and bit lines                         |  |  |  |  |  |

|      | 1  |     | $\bigcirc$ |    |      |

|------|----|-----|------------|----|------|

| VDD  |    | 1 ● | 54         | IJ | VSS  |

| DQO  |    | 2   | 53         |    | DQ15 |

| VDDQ |    | 3   | 52         |    | VSSQ |

| DQ1  |    | 4   | 51         | П  | DQ14 |

| DQ2  |    | 5   | 50         |    | DQ13 |

| VSSQ | T  | 6   | 49         | П  | VDDQ |

| DQ3  |    | 7   | 48         |    | DQ12 |

| DQ4  |    | 8   | 47         |    | DQ11 |

| VDDQ |    | 9   | 46         |    | VSSQ |

| DQ5  |    | 10  | 45         |    | DQ10 |

| DQ6  |    | 11  | 44         |    | DQ9  |

| VSSQ |    | 12  | 43         | П  | VDDQ |

| DQ7  |    | 13  | 42         |    | DQ8  |

| VDD  |    | 14  | 41         |    | VSS  |

| DQML |    | 15  | 40         |    | NC   |

| WE#  |    | 16  | 39         | П  | DQMH |

| CAS# |    | 17  | 38         | П  | CLK  |

| RAS# |    | 18  | 37         |    | CKE  |

| CS#  |    | 19  | 36         | П  | A12  |

| BAO  |    | 20  | 35         |    | A11  |

| BA1  |    | 21  | 34         |    | A9   |

| A10  | CL | 22  | 33         | Т  | 8A   |

| AO   |    | 23  | 32         |    | A7   |

| Al   |    | 24  | 31         |    | A6   |

| A2   |    | 25  | 30         |    | A5   |

| A3   |    | 26  | 29         |    | A4   |

| VDD  |    | 27  | 28         |    | VSS  |

#### Pin assignment

# Definition and Function of DRAM Pins

| Pin name          | Definition                        | Function                                                        |

|-------------------|-----------------------------------|-----------------------------------------------------------------|

| CLK               | Clock input                       | Reference system clock for the operation and data communication |

| CKE               | Clock Enable                      | Control the clock input                                         |

| $\overline{CS}$   | Chip Select                       | Activate the DRAM device from a memory cluster                  |

| RAS               | Row Address Strobe                | Latch row address and start the cell core operation             |

| CAS               | Column Address Strobe             | Latch column address and start the data communication operation |

| WE                | Write Enable                      | Activate the write operation                                    |

| A0 to A14         | Address input                     | Select a data bit                                               |

| DQ0 to DQ15       | Data input and output             | Communicate data with external devices                          |

| DQMU/DQML         | DQ Mask for Upper<br>(Lower) Byte | Mask byte data from the operations                              |

| $V_{DD}/V_{SS}$   | Power pins                        | Power for DRAM core and peripheral circuits                     |

| $V_{DD}Q/V_{SS}Q$ | Power pins                        | Power for DQ circuits                                           |

| NC                | No connection                     |                                                                 |

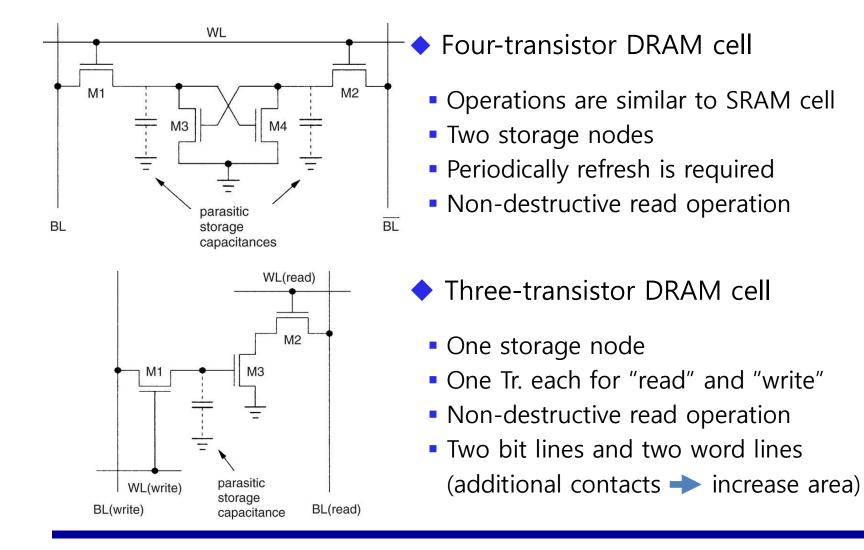

# Historical Evolution of DRAM Cell(1)

# Historical Evolution of DRAM Cell(2)

- Two-transistor DRAM cell

- Explicit storage cap.

- Destructive read operation (share with the bit line)

- Two bit lines and one word line

- One-transistor DRAM cell

- Industry-standard DRAM cell

- Destructive read operation (share with the bit line)

- Charge restoring operation required

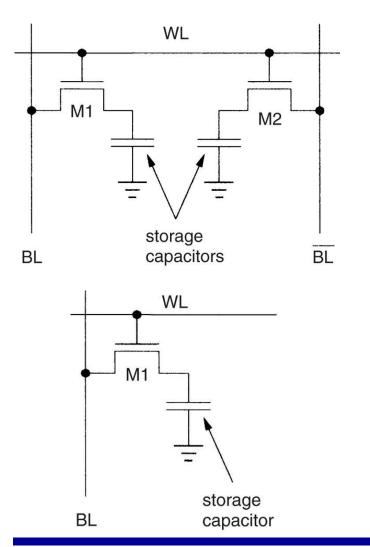

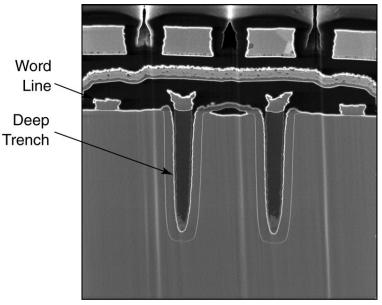

# DRAM Cell Types

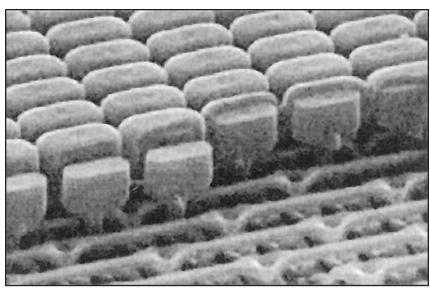

#### With only one transistor and one capacitor

- Smallest area of the all DRAM cells.

- Destructive "read" operation

- → major effort : large cap. cell with minimized area

(a) DRAM cell with a stacked cap.

(b) DRAM cell with a trench cap.

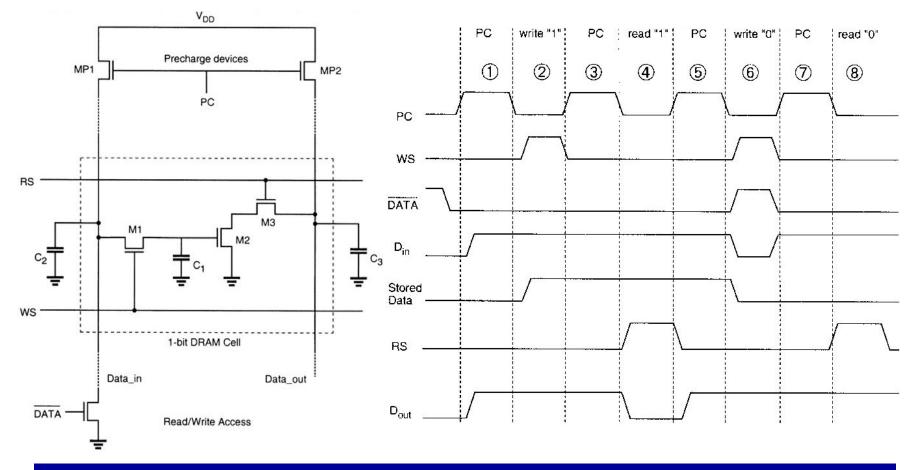

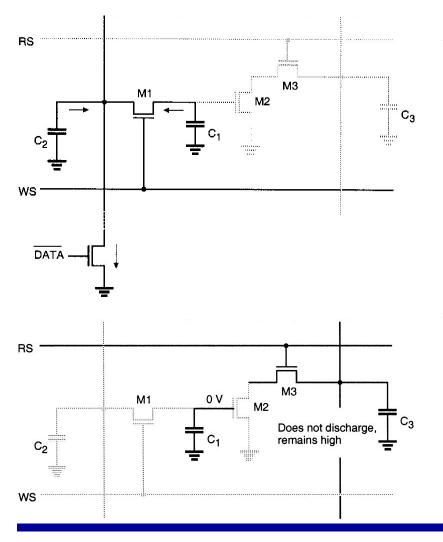

## **Operation of Three-Transistor DRAM Cell**

Typical 3-T DRAM cell and voltage waveforms

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

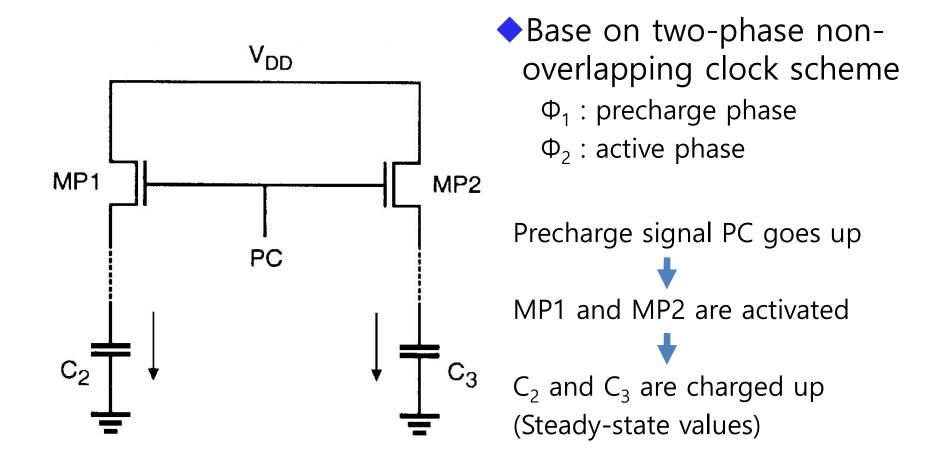

#### Precharge Events

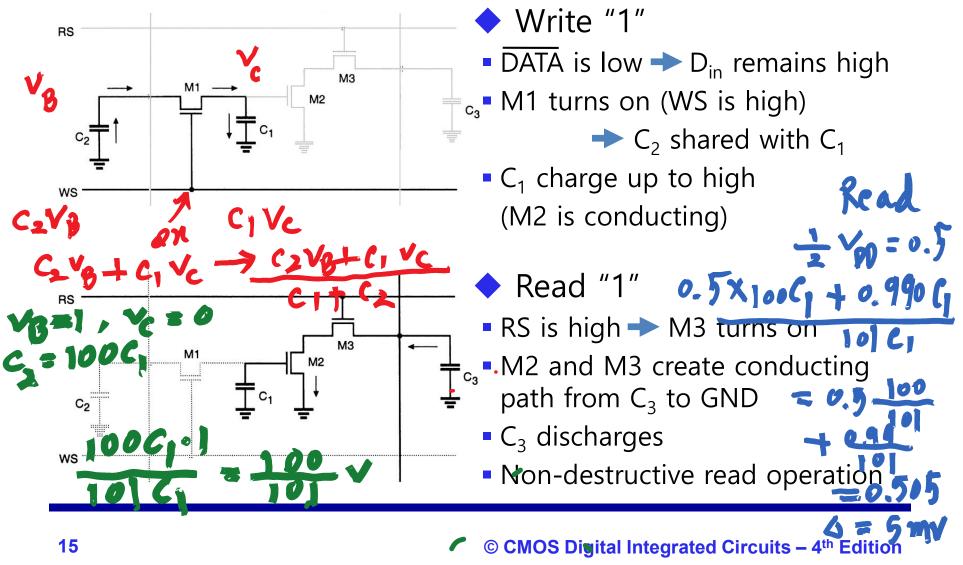

## Write "1" and Read "1" Operations

### Write "0" and Read "0" Operations

♦ Write "0"

• DATA is high  $\rightarrow$  D<sub>in</sub> goes low

- M1 turns on (WS is high)

- C<sub>1</sub> discharges (M2 turns off)

- Read "0"

- RS is high → M3 turns on

- No conducting path

- C<sub>3</sub> does not discharge

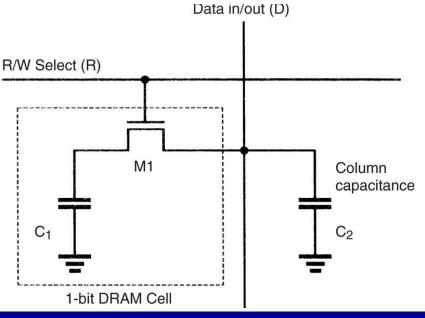

## **Operation of One-Transistor DRAM Cell**

One explicit storage cap. and one access transistor

- The most widely used storage structure

- Bit lines are folded and precharged to half-V<sub>DD</sub>

- → improve noise-immunity & reduce power consumption

- Operation : "read", "write", "refresh"

## 1-T DRAM Structure

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

18

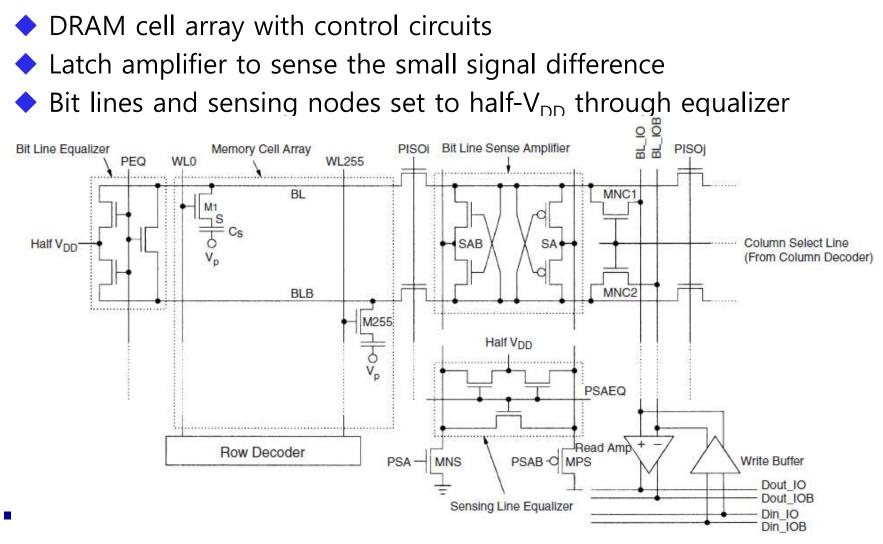

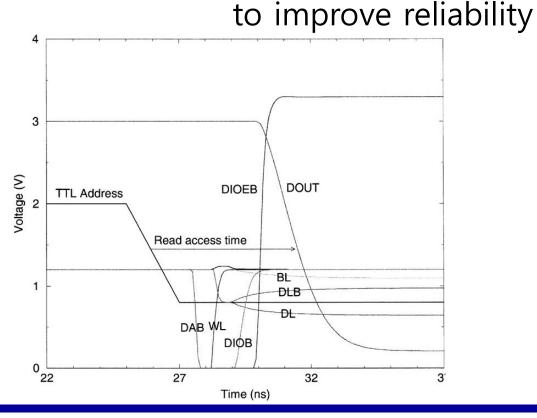

## DRAM Read Operation

PISOi Vpp Vpp  $C_{S}$  shared with  $C_{BI}$  (=initially half  $V_{DD}$ ) PISOi/PISO PISO VPP Word Line charge sharing between the cell and bit line capac cell data restoring Βl Voc BL/BLB 1/2Vpp BLB activation of  $V_{\text{DD}}$ hit line sense amplifier PSA VDD PSAB VDD Column Select BL IO BL\_IO/BL\_IOB BL\_IOB Dout IO Vdd Dout\_IO/ Dout\_IOB Word line 3 Voltage (V) **DRA234** DOUT BL IO 0\_20 40 60 80

Time (nS)

VDD

PEQ/PSAEQ

$\Delta V = \frac{C_s}{C_{p_l} + C_s} \frac{V_{DD}}{2}$  $\diamond$  C<sub>s</sub> : V<sub>DD</sub>  $\rightarrow$   $\frac{1}{2}$ V<sub>DD</sub> +  $\Delta$ V (destructive) BL and BLB voltage difference amplified  $BLB \rightarrow GND, BL \rightarrow V_{DD}$ storage node is recovered (restoring) Column switch is enabled by column

- decoder (BL -> BL\_IO, BLB -> BL\_IOB)

- Read Amp. amplifies the voltage difference

- $V_{PP} = V_{DD} + V_{th}$  for full charge restoration

- PSA and PSAB are sequentially activated to reduce charge injection and short circuit current

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

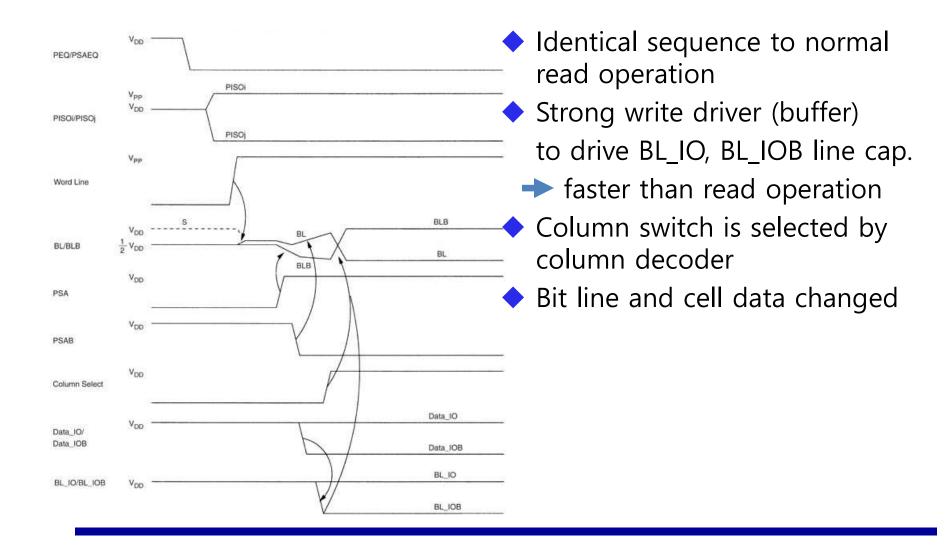

### **DRAM Write Operation**

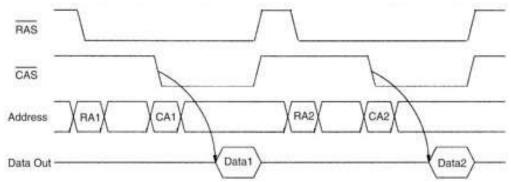

## Asynchronous DRAM Mode(1)

- single bit access (different row and column addresses)

- Operation uses address multiplexing scheme (RAS and CAS)

- reduce the chip package size

- ♦ RAS pull down → operation start

- RAS, CAS precharge before new data access

- $\diamond$  t<sub>RAC</sub> : memory read latency, time to read data from falling of  $\overline{RAS}$

- Length of word line is determined by refresh cycle constraint

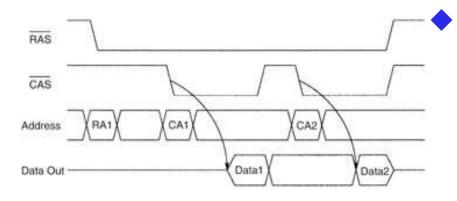

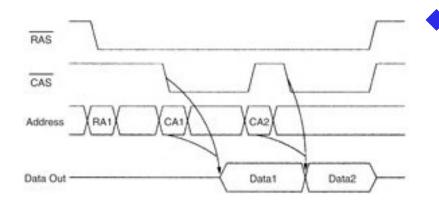

## Asynchronous DRAM Mode(2)

page access

- keep the row address

- read cell of same row address

- faster read operation

- extened data-out(EDO)

- new column address is captured at rising edge of CAS

- Read data maintain during precharge time

- Fastest read opertaion

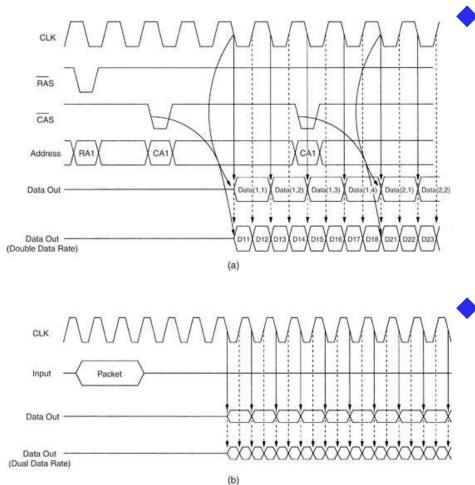

## Synchronous DRAM Mode

Four bit burst read

- Read frequency improve with use of the system clock

- At falling edge, control signal and addresses become active

- Pipelined based on clock to improve throughput

- Use both of edges to improve bandwidth (Dual Data Rate)

- Serial mode read

- Use small signal swing and clock recovery scheme to maximize the frequency

- Send control input as packet

- Send out data in a serial form

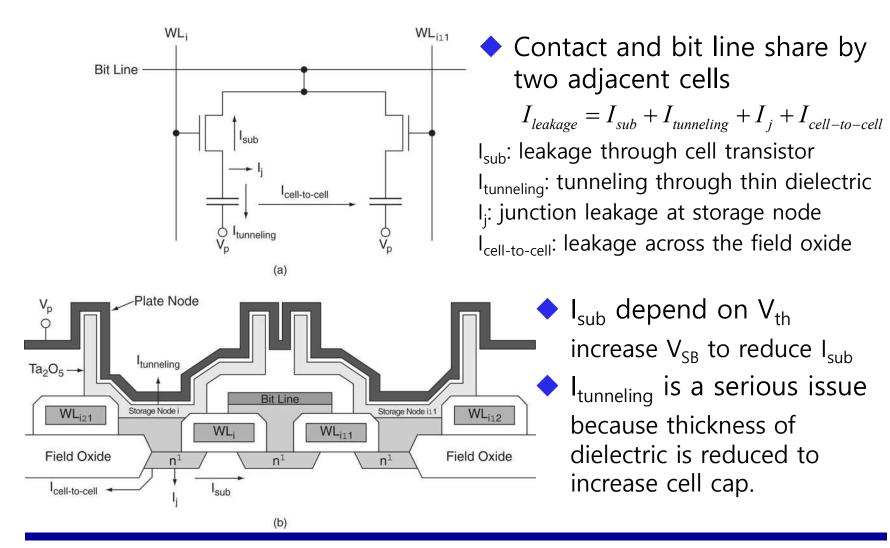

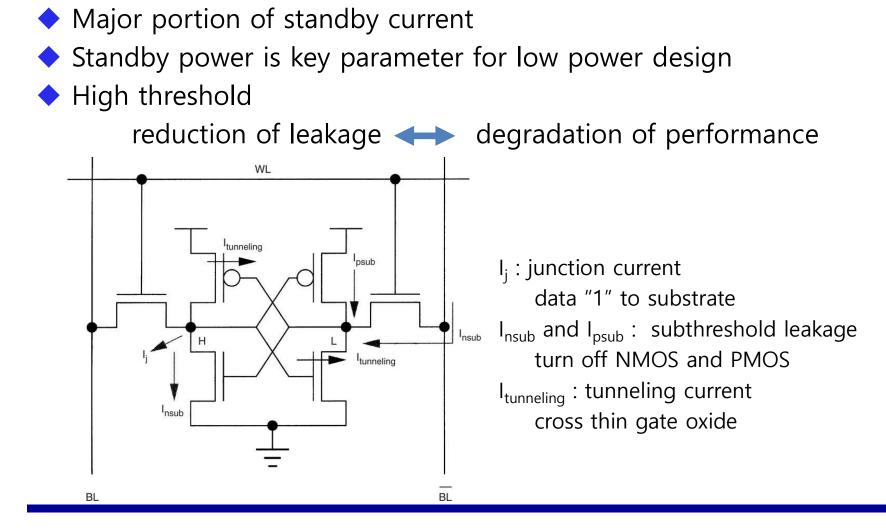

## Leakage Currents in DRAM Cells

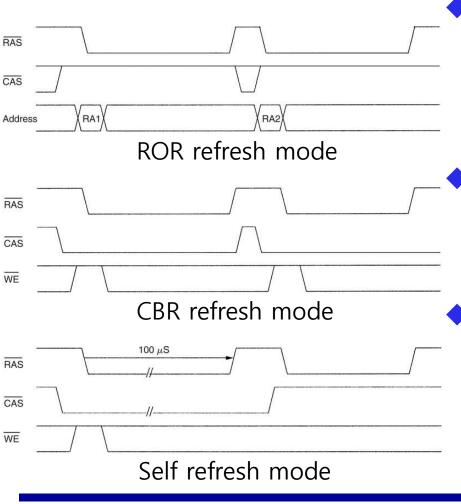

## **Refresh Operation**

ROR(RAS-only refresh) refresh

- Read and restore operation

- Does not send data out

- similar to normal read operation

- CBR(CAS-before-RAS) refresh

- row address generated by onchip counter

- performed periodically

- Self refresh

- period set according to operating condition

- row address and control signal generated by internal circuit

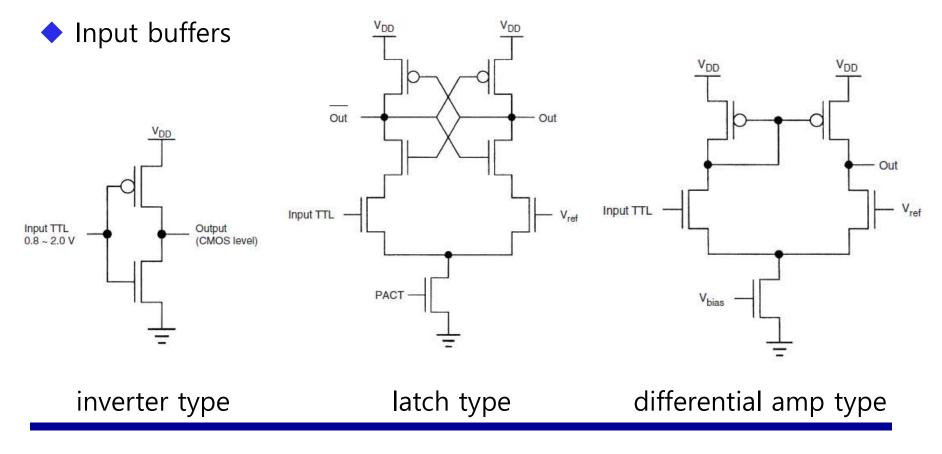

## DRAM Input/Output Circuits(1)

Logic level of system board and memory chip are different

required to convert logic levels

input/output buffers

# Characteristic Comparison of Input Buffers

|                                                     | Buffer type                                |                                               |              |

|-----------------------------------------------------|--------------------------------------------|-----------------------------------------------|--------------|

|                                                     | Inverter                                   | Latch                                         | Differential |

| Logic threshold determination $(V_{IH} and V_{IL})$ | By W <sub>P</sub> /W <sub>N</sub><br>ratio | By V <sub>ref</sub>                           | By $V_{ref}$ |

| Speed                                               | Slow                                       | Fastest                                       | Fast         |

| Standby current                                     | Small                                      | Smallest                                      | Large        |

| Sensitivity to V <sub>DD</sub> and temperature      | Large                                      | Small                                         | Small        |

| Noise immunity                                      | Bad                                        | Good                                          | Good         |

| Constraint                                          | None                                       | Precharge and<br>activation signals<br>needed | None         |

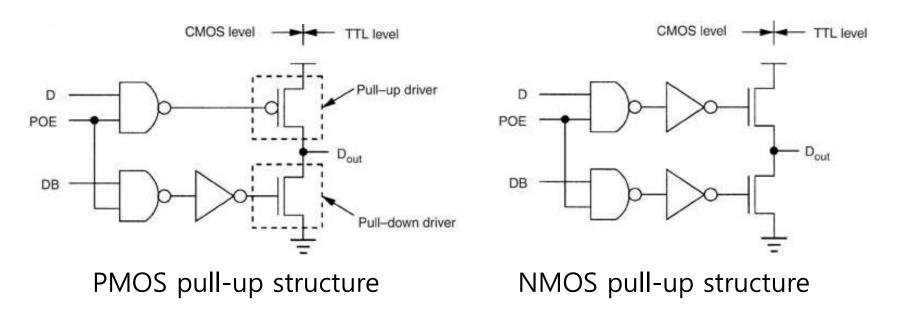

## DRAM Input/Output Circuits(2)

#### Memory output buffers

- Need to drive large cap.

- Keep a high-impedance when chip is not selected

- → to prevent interference of output

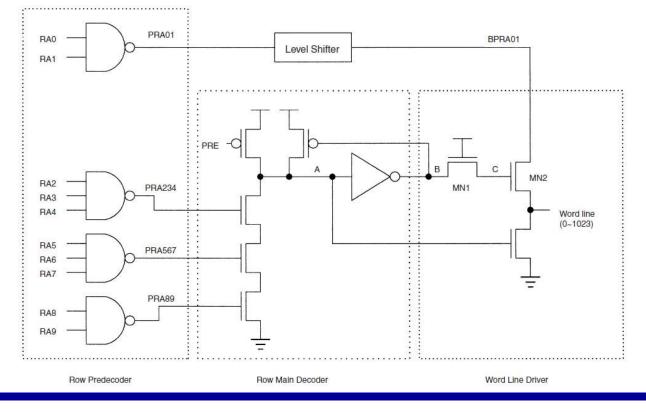

### DRAM Decoder(1)

To select cell from 2<sup>2M</sup> memory array, M address bits are needed

Practically, M transistors in series is impossible

decoding scheme is composed of pre and main decoder

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

## DRAM Decoder(2)

## Voltage Sense Amplifiers

#### To detect signal difference on data lines

OUT

OUT

- Current-mirror differential

- Popular and good common-mode rejection ratio

- Large area and large power consumption

#### Full CMOS latch type

- High speed, small area and low power

- Precharge signal required

- operation cannot be reversed

- Semilatch type

- Between current-mirror type and full CMOS latch type

OUT -C

ĪN

PSAF

IN

PSAE

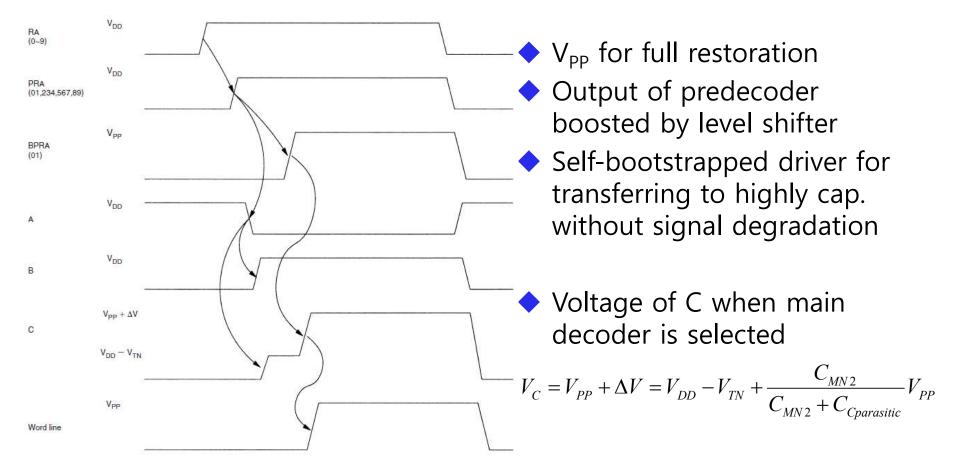

## Internal Voltage Regulator Circuit

Lowering voltage to reduce power consumption

V<sub>INT</sub>(internal voltage generator)

reduce operating current

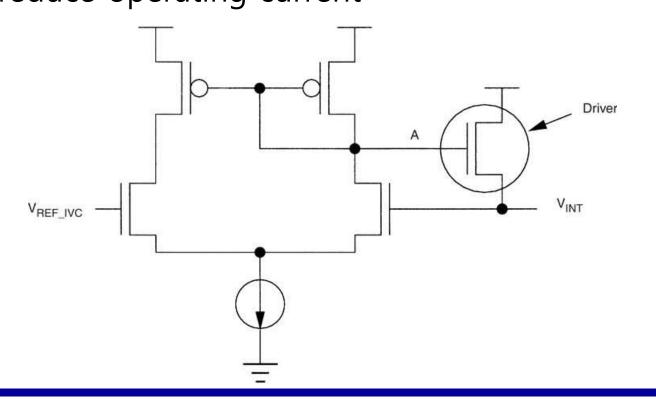

# Half V<sub>DD</sub> Voltage Generator

Folded bit line structure with half V<sub>DD</sub> sensing scheme

- Improve noise immunity and low power consumption

- Reduce electric field across thin dielectric

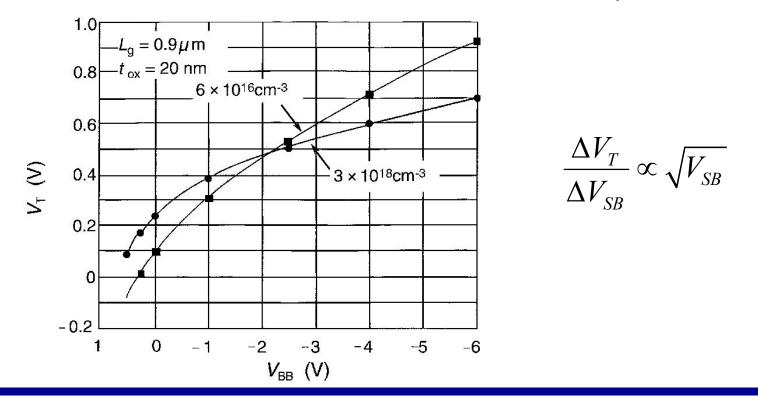

#### Negative Substrate Bias Voltage Generator(1)

Subthreshold current is major source of charge decay

Negative voltage substrate -> increase threshold voltage

➡ reduce load cap. of bit line

#### Negative Substrate Bias Voltage Generator(2)

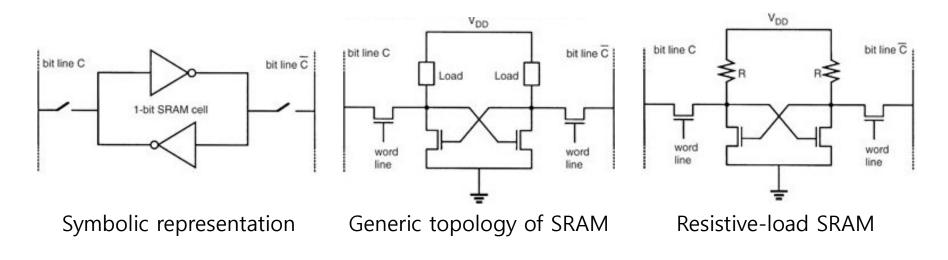

## 10.3 Static Random Access Memory(1)

- Stored data can be retained indefinitely

- Simple latch with two stable operating points

- Two access switches to connect 1-bit SRAM

- Poly resistor load inverter structure is more compact cell size (resistor stack on top of cell)

- ◆ Load R trade off : low power ← wider noise margin, high speed

## 10.3 Static Random Access Memory(2)

#### Depletion-load NMOS SRAM

Six-transistor

(one poly and one metal layer)

- Cell size relatively small

- Static characteristics and noise margins better than resistive-load cell

- Static power consumption

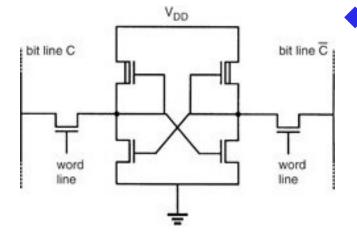

#### Full CMOS SRAM

- Most popular

- Lowest static power

- Superior noise margins and switching speed

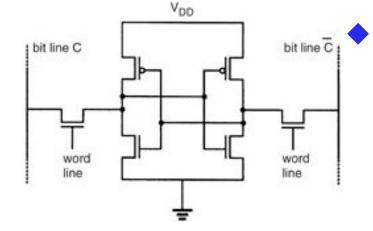

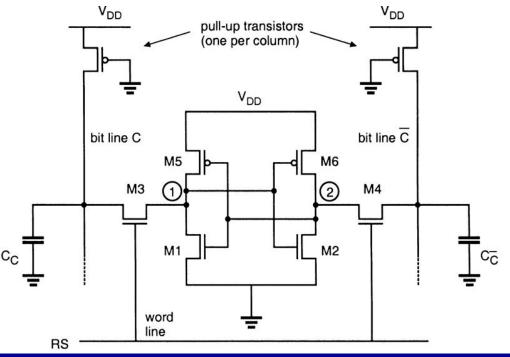

# Full CMOS SRAM Cell(1)

- Very small static power dissipation (limited by leakage current)

- High noise immunity (large noise margin)

- Ability to operate at lower supply

- Disadvantage : cell area slightly larger, latch-up phenomena

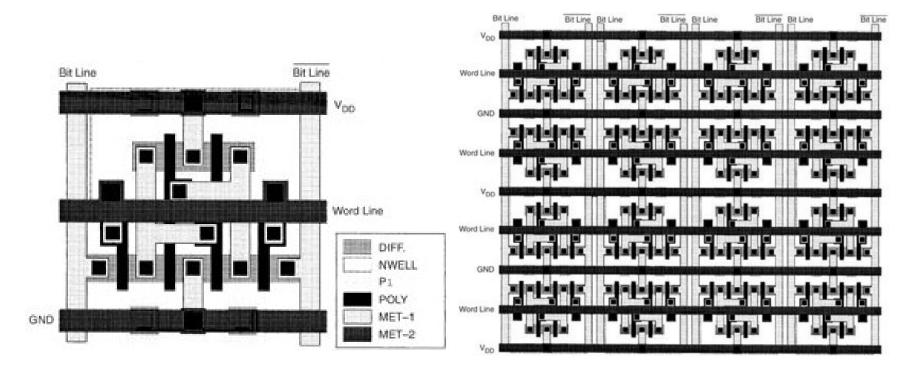

#### Full CMOS SRAM Cell(2)

Layout of CMOS SRAM cell

Layout of a 4-bit X 4bit SRAM array, consisting of 16 CMOS SRAM cells

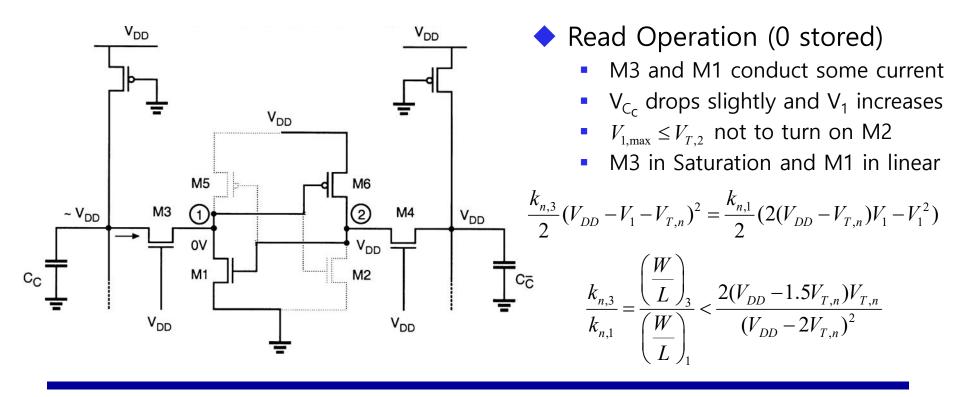

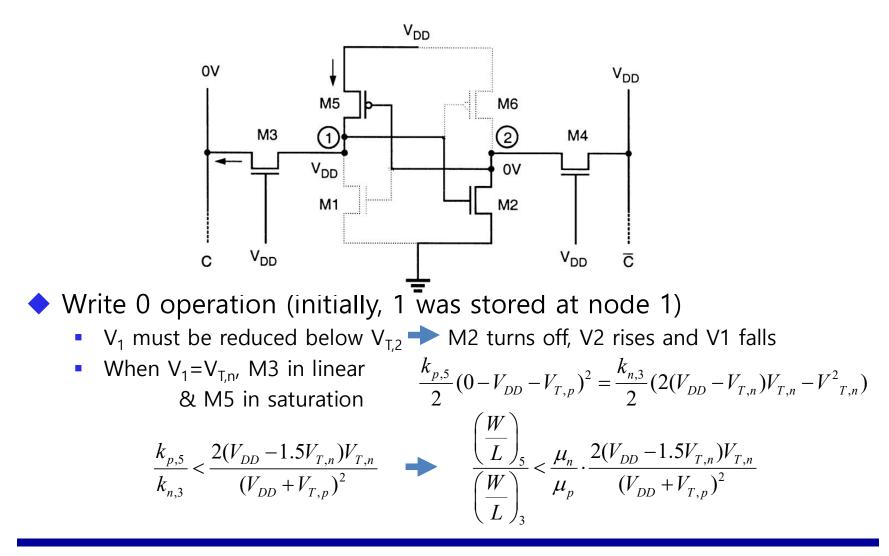

# CMOS SRAM Cell Design Strategy(1)

Two basic requirements which dictate W/L ratio

- Non-destructive data read operation

- Modify stored data during write phase

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

#### CMOS SRAM Cell Design Strategy(2)

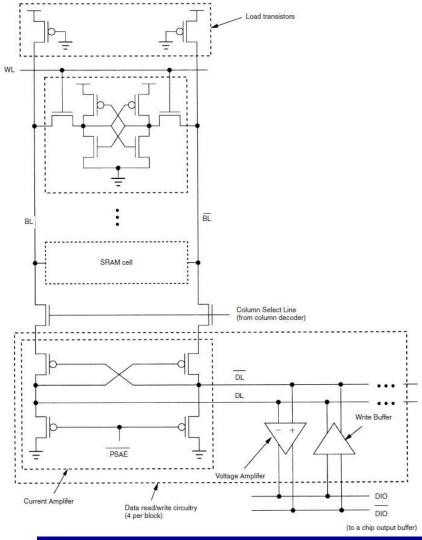

# Memory Structure of SRAM

- Word line selected by row address

- Cell data kept during read operation

- Boosted voltage not required

- Address multiplexing scheme is not used (fast access time than DRAM)

- Depend on applications

- ultra low power : load transistor turns off during read operation

- high speed : remains on

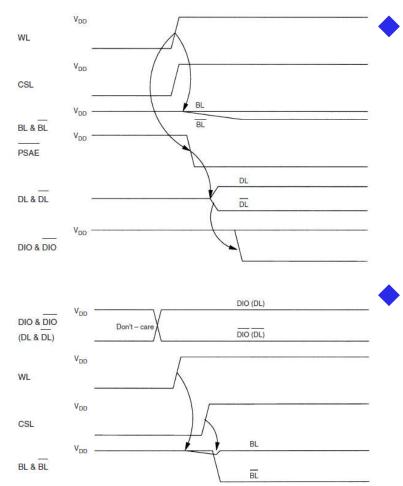

## **Operation of SRAM**

#### Read operation

- Word line enable

- One bit line discharge (voltage change of bit line is very small)

- Sense amp. detect the voltage difference on bit line

- Multi-stage amp. is used to improve read speed

- Write operation

- Word line selected by row address

- Write buffer write data into cell

- Write buffer has larger current driving capability than cell

- Write is faster than read

#### SRAM Read Operation

TTL level converts into CMOS level signal

Internal voltage regulator to reduce power dissipation

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

### Leakage Currents in SRAM Cells

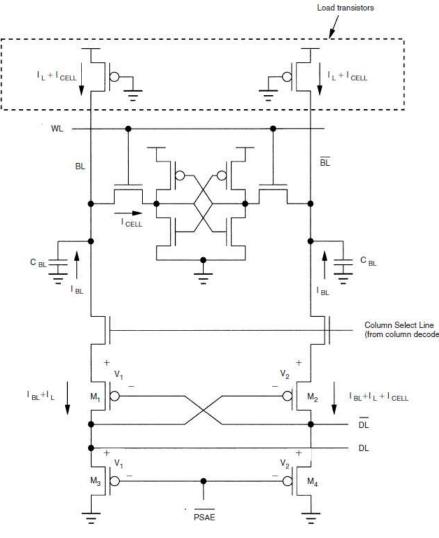

### SRAM Read/Write Circuits

- Current-mode sense amp widely used in SRAM

- improve signal sensing speed independent of bit line cap.

- Signal line connect to source of latch transistor

- Current difference appears on DL and DL

- Open-loop gain  $Gain_{open-loop} = \frac{g_m(m3) \times g_m(m4)}{g_m(m1) \times g_m(m2)}$

- Current-mode sense amp: Drawback- larger power consumption

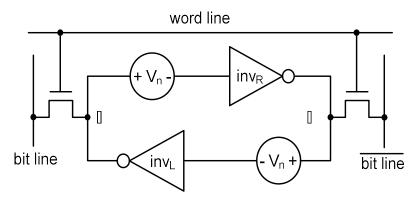

# SRAM Cell at Low Supply Voltage

#### SRAM cell susceptible to variabilities

- Due to minimum device size to a minimize area

- Threshold voltage variation covered in Ch. 3 plus layout induced threshold voltage variation

- PMOS pair (M5, M6) in SRAM cell- different  $V_T$  due to NBTI

- NMOS pair (M1, M2) in SRAM cell- different  $V_T$  due to PBTI

- Static noise margin (SNM)

- A noise tolerant voltage before the stored data flip

- Equivalent ckt to measure SNM

- 6-T SRAM cell at low supply voltage degrades SNM

V<sub>n</sub>: DC noise, SNM: min. DC noise which flips the state of SRAM cell during read operation

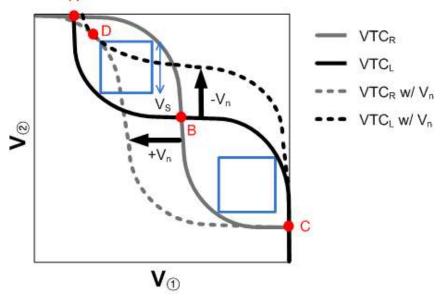

# SNM Variation due to DC Noise

How to measure SNM graphically

- SNM: The length of side of the smaller nested square in the two openings of butterfly curve

- Before two V<sub>n</sub>s are fed: SNM=V<sub>s</sub>

- After V<sub>n</sub>s are fed: stable point A and unstable point B meets at D

- More V<sub>n</sub>s are applied: one common point C & the stored bits are flipped

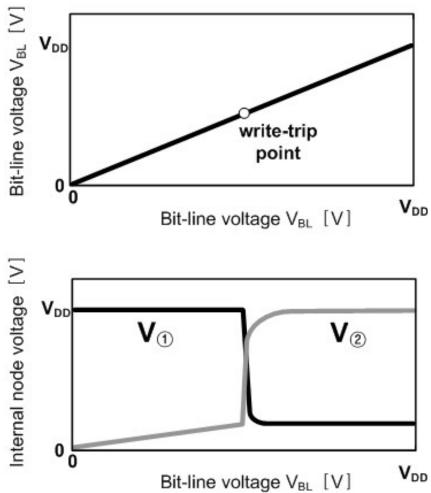

#### SRAM Cell Writability

#### 🔷 Write-trip point

- A metric for writability

- Max. bit line voltage to flip the state of the SRAM cell

- Primarily determined by the pull-up ratio of SRAM cell (Ex: (W/L)<sub>5</sub>/(W/L)<sub>3</sub>)

- Variability tolerant 6T

SRAM cell

- Trade off bw. read stability and writability

- $M_3 \& M_4 \uparrow$ : SNM ↑, writability ↓

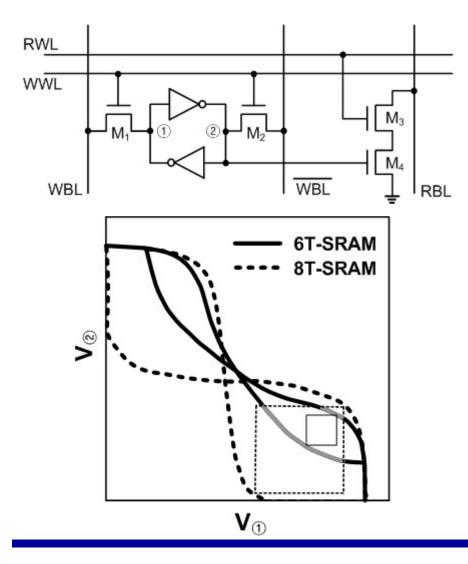

### 8T SRAM Cell

- No secondary power supplies

- Decouples the SRAM cell nodes from the bit line which enables balancing the read & write modes

- Read operation doesn't affect the stored data

- 6T cell has the worst SNM in read operation where the pass gate transistor increases the voltage at the '0' stored

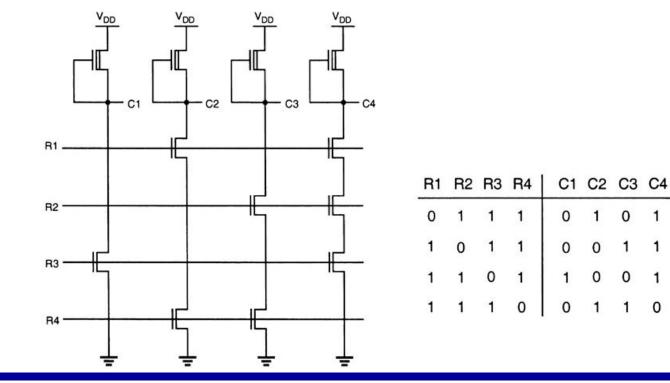

#### 10.4 Nonvolatile Memory

- Simple combinational Boolean network

- Only one word line selected at a time

- Active transistors exist at cross point

- Dynamic ROM

- use periodic precharge signal to reduce static power

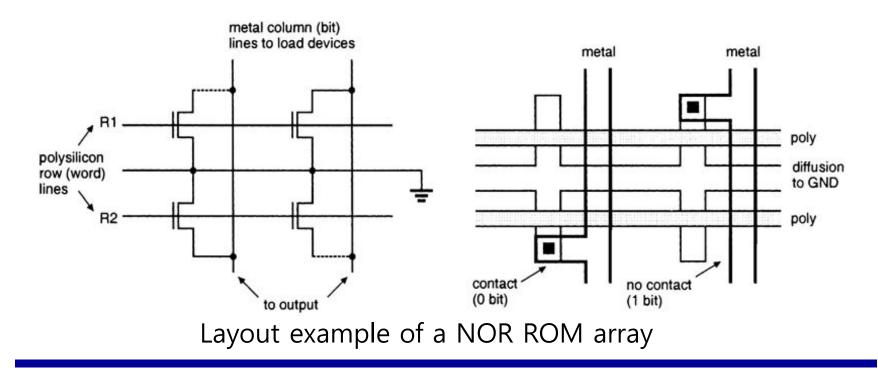

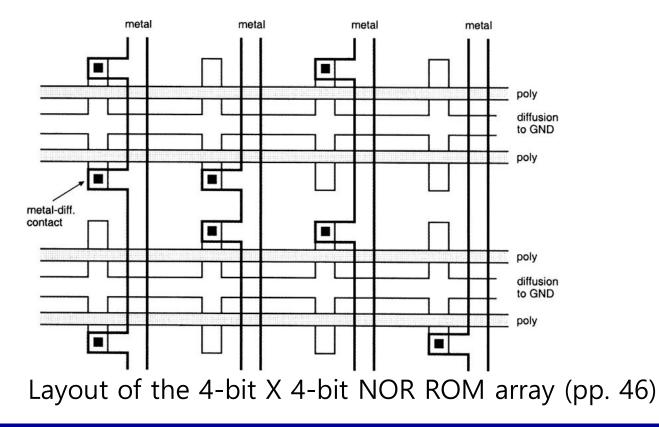

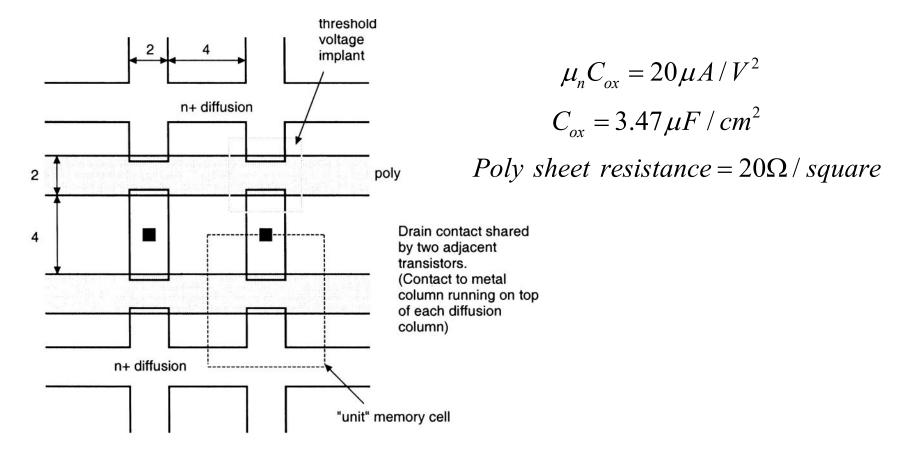

# Layout of NOR ROM Array(1)

Initially, NMOS at every row-column intersection

'1'-bits are realized by omitting drain or source connection or gate electrode of corresponding NMOS

## Layout of NOR ROM Array(2)

In reality, metal column lines laid out directly on top of diffusion column to reduce horizontal dimension

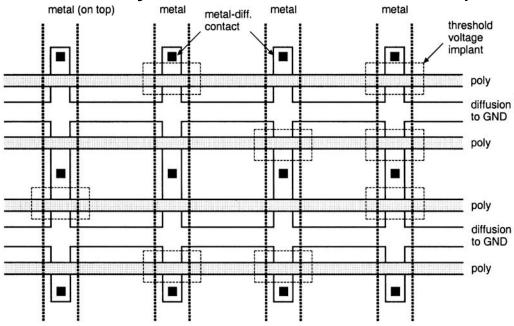

#### Implant-mask Programmable NOR ROM

Every two rows share a common ground connection

Every metal to diffusion contact shared by two adjacent devices

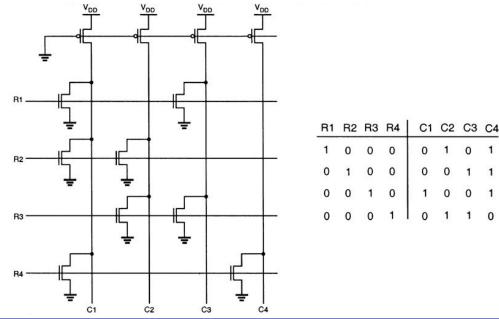

#### 4-bit x 4-bit NOR ROM Array

Based on implant-mask programming

◆ Raised threshold voltage >V<sub>OH</sub> → "1"-bit

◆ Non-implanted → "0"-bit

higher core density (smaller silicon area per stored bit)

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

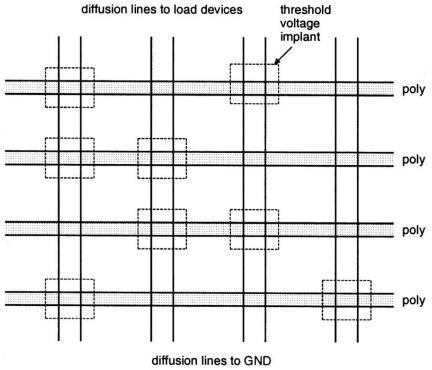

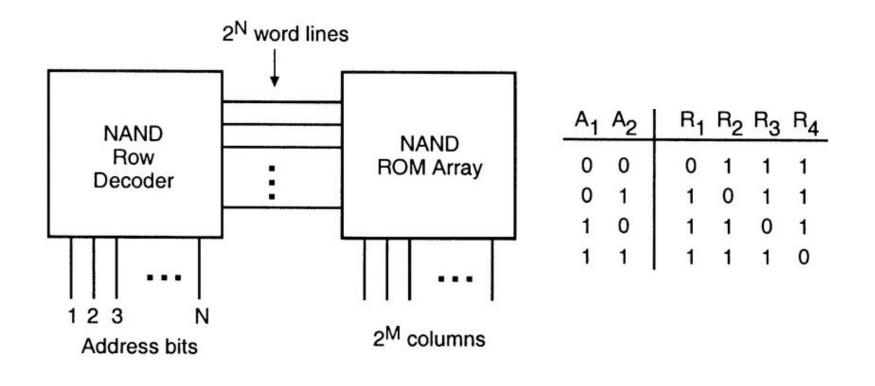

#### 4-bit x 4-bit NAND ROM Array

Bit line : depletion-load NAND gate

Deactivated transistor → "1"-bit

Shorted or on transistor -> "0"-bit

#### Implant-mask layout of NAND ROM

Lowered threshold voltage < 0V → "0"-bit</li>

Much more compact than NOR ROM

Access time is slower than NOR ROM

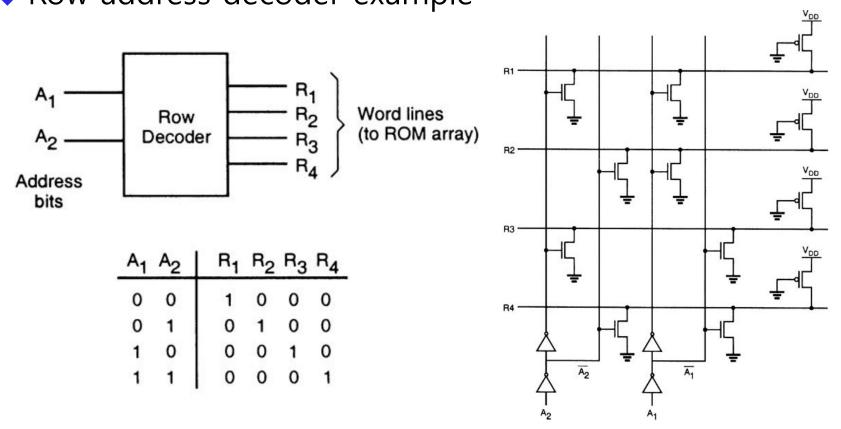

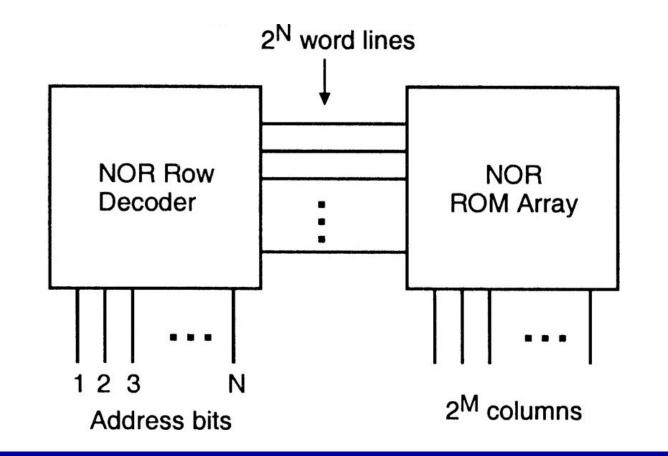

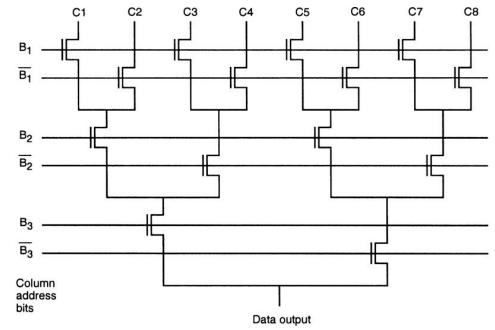

### Design of Row and Column Decoders(1)

Select a particular memory location in array

Row address decoder example

# Design of Row and Column Decoders(2)

ROM array and row decoder (two adjacent NOR arrays)

#### Row Decoder for NAND ROM

Lower voltage for logic "0"

Realized using same layout strategy as memory array

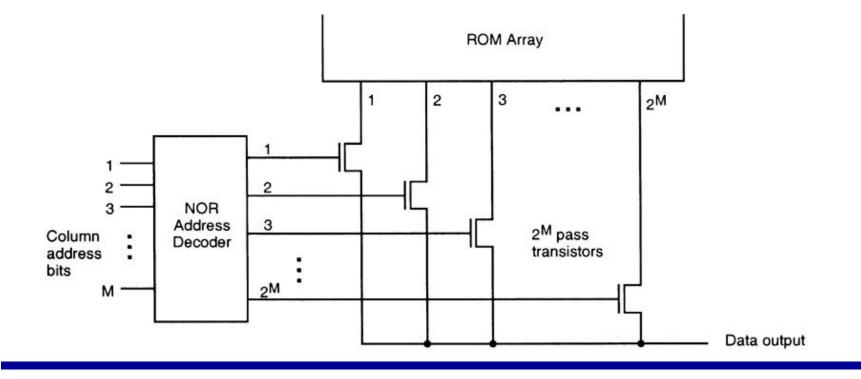

## Column Decoder(1)

Using NOR address decoder and NMOS pass transistor

Only one pass transistor turned on at a time

2<sup>M</sup>(M+1) transistors required

## Column Decoder(2)

Binary selection tree decoder

NOR address decoder not needed

Reduce the number of transistors significantly

But, long data access time

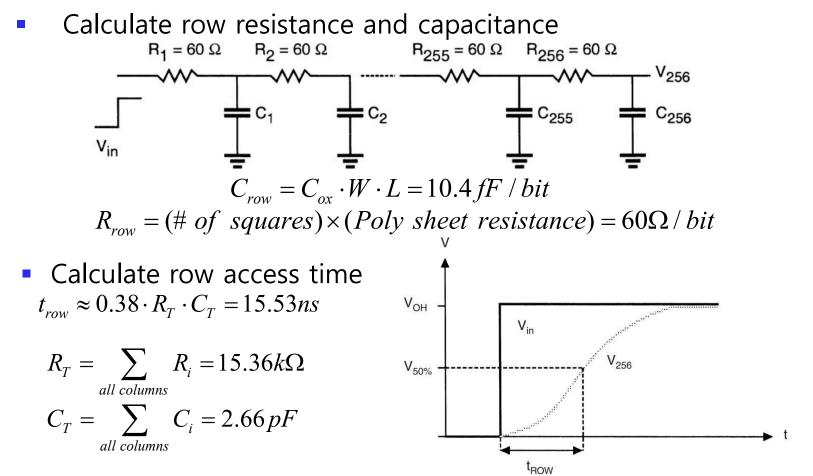

#### Example 10.1(1)

Analyze the access time of a 32-kbit NOR ROM array

# Example 10.1(2)

Assume 7 row address bits and 8 column address bits (128 rows and 256 columns)

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

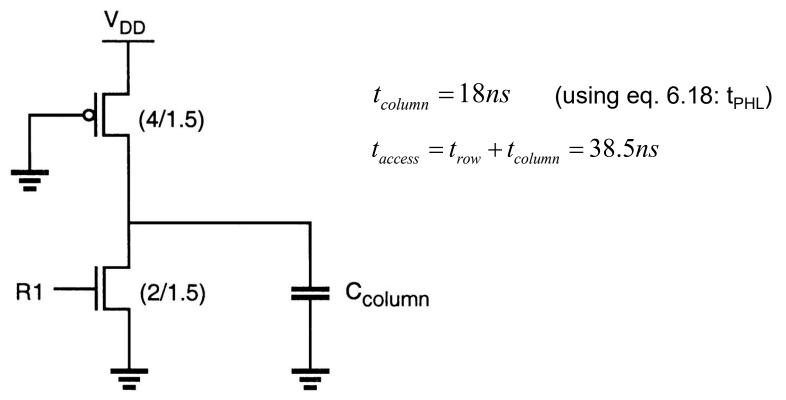

#### Example 10.1(3)

A more accurate delay: Elmore time constant for RC ladder circuits

$$t_{row} = \sum_{k=1}^{256} R_{jk} C_k = 20.52 ns$$

where  $R_{jk} = \sum_{j=1}^{k} R_j$

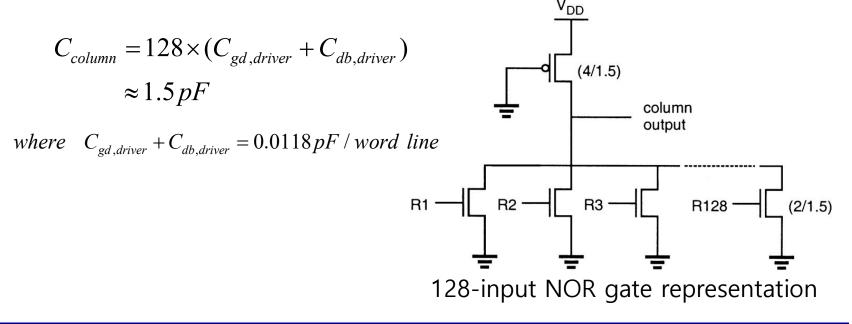

Calculate column access time

#### Example 10.1(4)

• To calculate column access time, consider the worst-case signal propagation delay  $\tau_{PHL}$  for below inverter

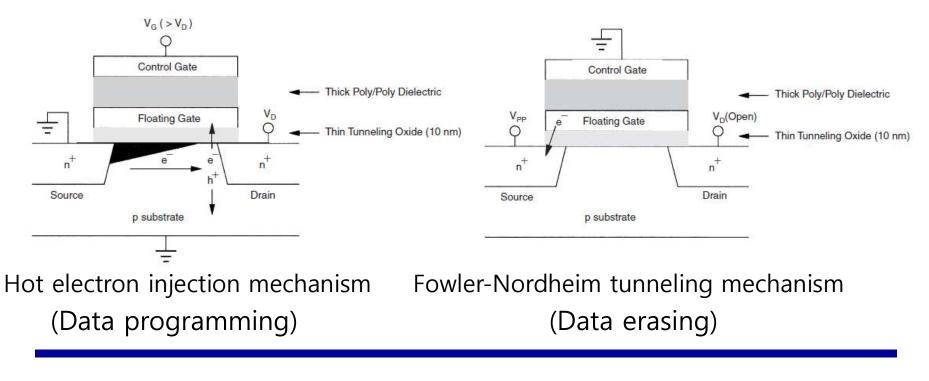

## 10.5 Flash Memory

- One transistor with floating gate

- Memory cell can have two states (two threshold)

- $\diamond$  Electron accumulated at the floating gate  $\rightarrow$  higher threshold  $\rightarrow$  "1" state

- Electron removed from the floating gate  $\rightarrow$  lower threshold  $\rightarrow$  "0" state

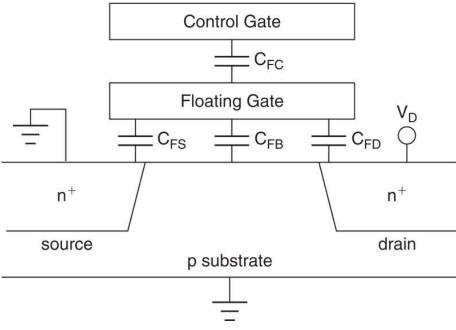

# Equivalent Capacitive-Coupling Circuit

$Q_{\text{FC}}$  : charge stored at floating gate

C<sub>total</sub> : total cap.

$C_{FC}$  : cap. between floating and control gate

$C_{FS^\prime}$   $C_{FB}$  and  $C_{FD}$  : cap. between floating gate and source, bulk and drain

$V_{CG}$  and  $V_{D}$  : voltage at control gate and drain

$V_{\rm T}({\rm FG})$  : threshold voltage to turn on the floating gate transistor

V<sub>FG</sub> by capacitive coupling after V<sub>CG</sub> & V<sub>D</sub> applied

$$V_{FG} = \frac{Q_{FG}}{C_{total}} + \frac{C_{FC}}{C_{total}} V_{CG} + \frac{C_{FD}}{C_{total}} V_{D}$$

$$C_{total} = C_{FC} + C_{FS} + C_{FB} + C_{FD}$$

min. V<sub>CG</sub> to turn on the control gate transistor

$$V_T(CG) = \frac{C_{total}}{C_{FC}} V_T(FG) - \frac{Q_{FG}}{C_{FC}} - \frac{C_{FD}}{C_{FC}} V_D$$

$$\Delta V_T(CG) = -\frac{\Delta Q_{FG}}{C_{FC}}$$

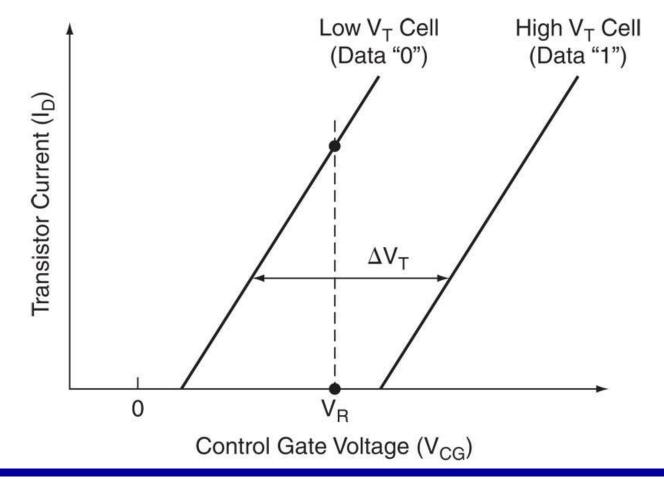

#### I-V Characteristic of Flash Memory

Low and high threshold voltages for control gate voltage

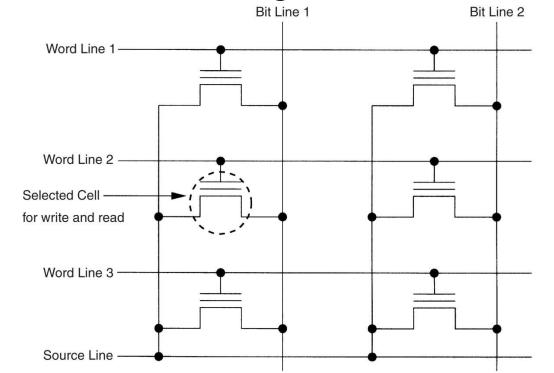

## NOR Flash Memory Cell

Bias conditions and configuration of NOR Cells

F-N tunneling mechanism for erase operation

Hot-electron injection mechanism for programming operation

# Bias Conditions of NOR Cell

|             | Operation |             |      |

|-------------|-----------|-------------|------|

| Signal      | Erase     | Programming | Read |

| Bit line 1  | Open      | 6V          | 1V   |

| Bit line 2  | Open      | 0V          | 0V   |

| Source line | 12V       | 0V          | 0V   |

| Word line 1 | 0V        | 0V          | 0V   |

| Word line 2 | 0V        | 12V         | 5V   |

| Word line 3 | 0V        | 0V          | 0V   |

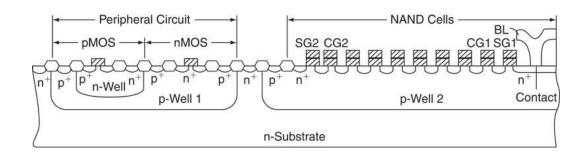

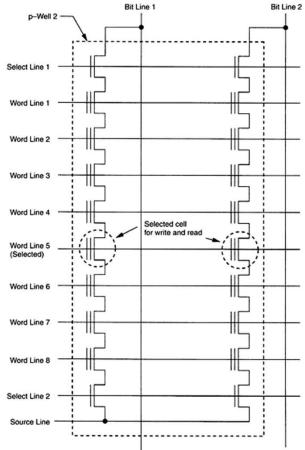

## NAND Flash Memory Cell

Cross-section view and configuration of NAND cells

F-N tunneling mechanism for erase

F-N tunneling mechanism for program

Slower programming and read speed but smaller area than NOR cell structure

#### Bias Conditions of NAND Cell

|               |       | Operation   |      |  |

|---------------|-------|-------------|------|--|

| Signal        | Erase | Programming | Read |  |

| Bit line 1    | Open  | 0V          | 1V   |  |

| Bit line 2    | Open  | 0V          | 1V   |  |

| Select line 1 | Open  | 5V          | 5V   |  |

| Word line 1   | 0V    | 10V         | 5V   |  |

| Word line 2   | 0V    | 10V         | 5V   |  |

| Word line 3   | 0V    | 10V         | 5V   |  |

| Word line 4   | 0V    | 10V         | 5V   |  |

| Word line 5   | 0V    | 20V         | 0V   |  |

| Word line 6   | 0V    | 10V         | 5V   |  |

| Word line 7   | 0V    | 10V         | 5V   |  |

| Word line 8   | 0V    | 10V         | 5V   |  |

| Select line 2 | Open  | 0V          | 5V   |  |

| Source line   | Open  | 0V          | 0V   |  |

| p-well 2      | 20V   | 0V          | 0V   |  |

| n-sub         | 20V   | 0V          | 0V   |  |

# Comparison between NOR and NAND

|                    | NOR                    | NAND          |

|--------------------|------------------------|---------------|

| Erase method       | F-N tunneling          | F-N tunneling |

| Programming method | Hot electron injection | F-N tunneling |

| Erase speed        | Slow                   | Fast          |

| Program speed      | Fast                   | Slow          |

| Read speed         | Fast                   | Slow          |

| Cell size          | Large                  | Small         |

| Scalability        | Difficult              | Easy          |

| Application        | Embedded system        | Mass storage  |

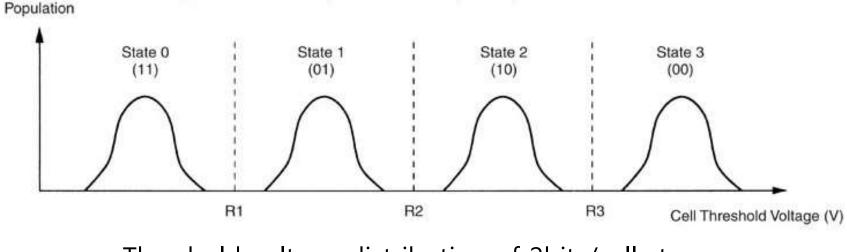

# Multilevel Cell Concept

Effective memory density can be improved

Possible state number limited by

- Available charge range

- Accuracy of programming and read operations

- Disturbance of state over time

Threshold voltage distribution of 2bits/cell storage

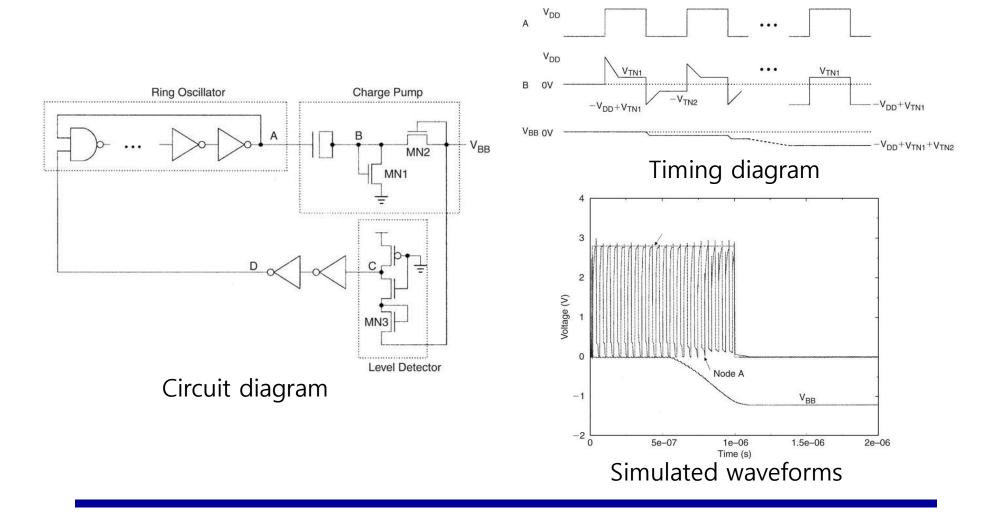

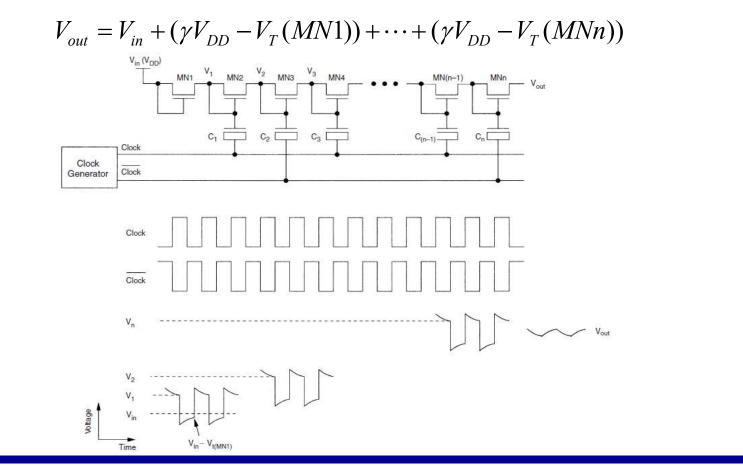

### Flash Memory Circuit

On-chip charge pump used to generate programming voltage

Chain of diode and cap. to charge or discharge each half cycle

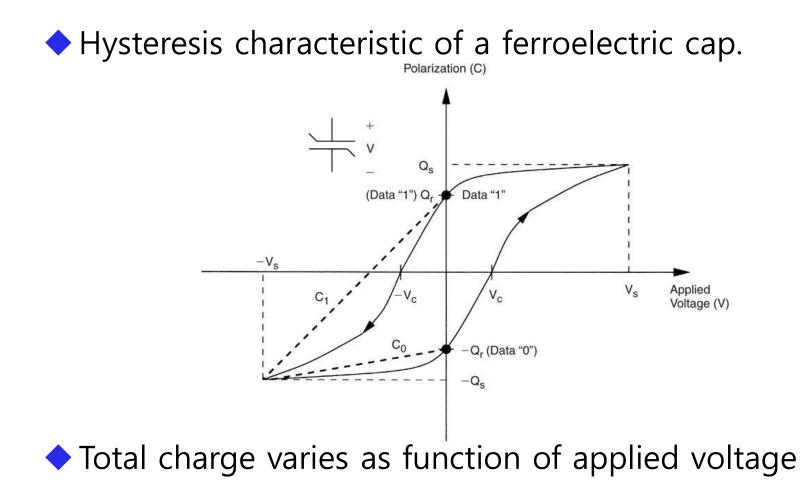

## 10.6 Ferroelectric Random Access Memory

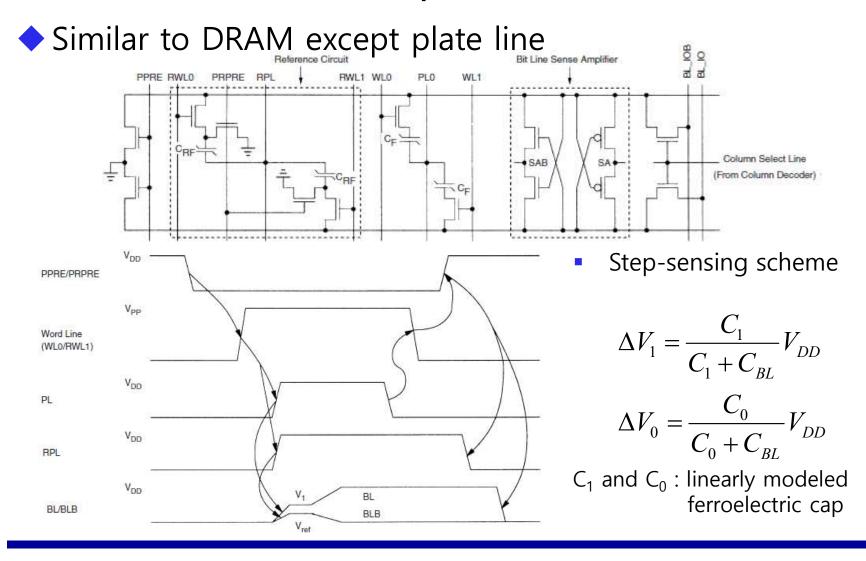

#### Structure and Operation of FRAM

#### Problems of FRAM

Step-sensing scheme cause reliability issues

- Pulse sensing scheme also used with read speed penalty

- ♦ Fatigue

- Capacitance charge gradually degraded with repeated use

#### Imprint

Ferroelectric cap tends to stay at one state preferably when state maintained for a long time