#### ECE 222 F 19 vecture 15 The McGraw-Hill Companies

#### **CMOS Digital Integrated Circuits**

1

Chapter 13 Chip Input and Output (I/O) Circuits

S.M. Kang, Y. Leblebici, and C. Kim

Copyright @ 2014 McGraw-Hill Education. Permission required for reproduction or display.

# Introduction

Critical factors of reliability, signal integrity, and interchip communication speed

- Clock generation and distribution

- External clock source -> on-chip internal clock generation

- ESD protection

- Protection for internal circuits from external hazards

- I/O circuits

- CMOS <-> TTL or ECL

- On-chip noise prevention

- From parasitic inductance in bonding wires

- Latch-up prevention

- From parasitic bipolar transistors

#### **ESD** Protection

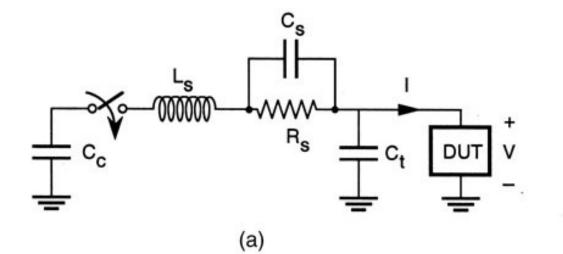

# Simplified Lumped-Element Model of HBM-ESD and MM-ESD Testers

| Component           | HBM  | MM  |

|---------------------|------|-----|

| C <sub>C</sub> (pF) | 100  | 200 |

| R <sub>s</sub> (Ω)  | 1500 | 25  |

| L <sub>S</sub> (µH) | 5    | 2.5 |

| C <sub>s</sub> (pF) | 1    | 0   |

| Ct(pF)              | 10   | 10  |

(b)

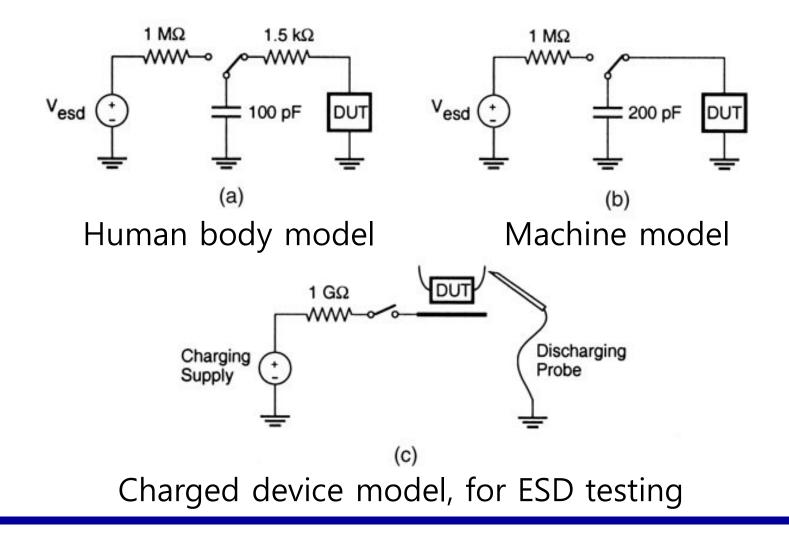

# Types of ESDs

HBM(Human Body Model)

- Human body can induce 1.5kV

- Condition

- 80% relative humidity

- Walking on synthetic carpet

MM(Machine Model)

- Higher current than HBM

- CDM(Charged Device Model)

- Discharge of the packaged IC

- Chip assembly or shipping -> Charge accumulation -> Discharge

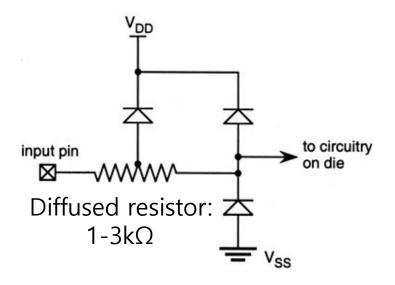

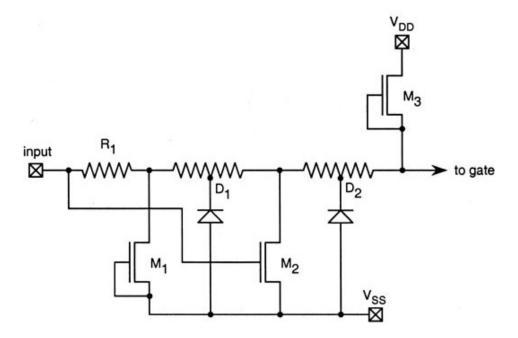

# **ESD** Protection Network Examples

Basic ESD protection network: diodes clamp the signal level  $-0.7V < V_A < V_{DD} + 0.7V$  $I_D <$  several tens of mA

Protection network with thick-oxide transistor: effective in excess of 3kV in HBM-ESD test

$M_1$ ,  $M_2$ : thick oxide device w/  $V_T$  of 20~30V  $M_3$ : thin oxide device operating in SAT region

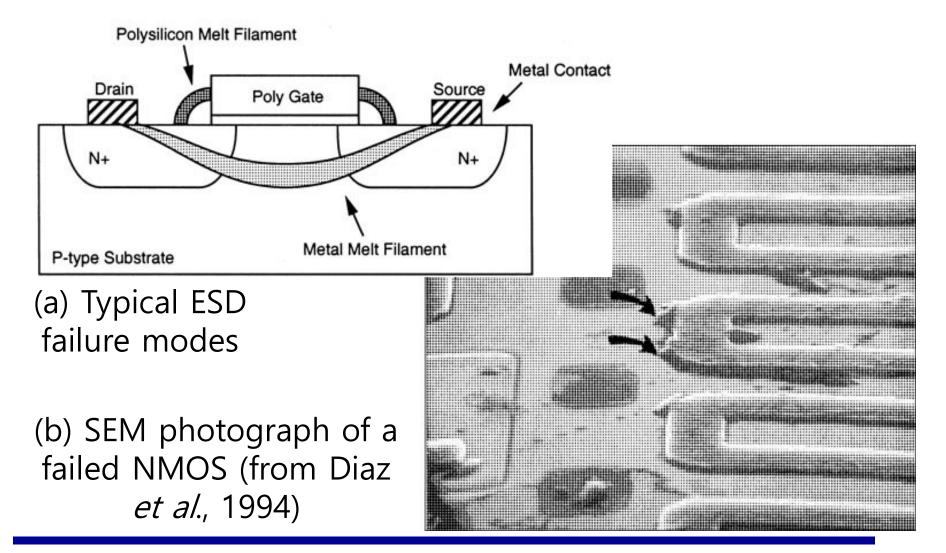

# **ESD** Failure

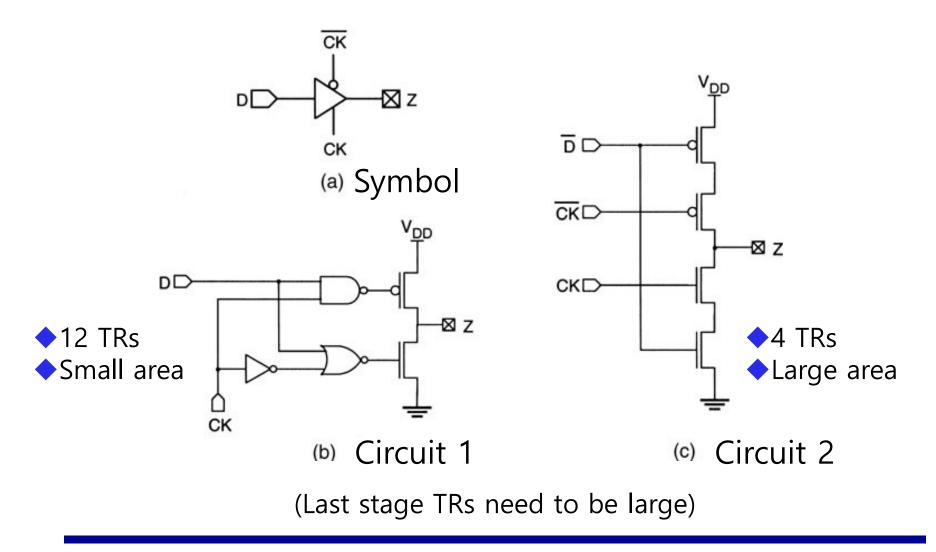

# Input Series Transmission Gate

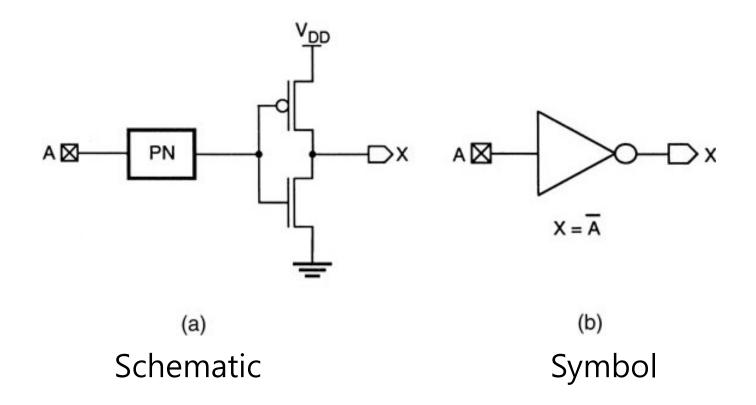

# Inverting Input Circuit with PN

- typical V<sub>IL</sub>=0.3V<sub>DD</sub>, V<sub>IH</sub>=0.7V<sub>DD</sub> for 30% noise margin

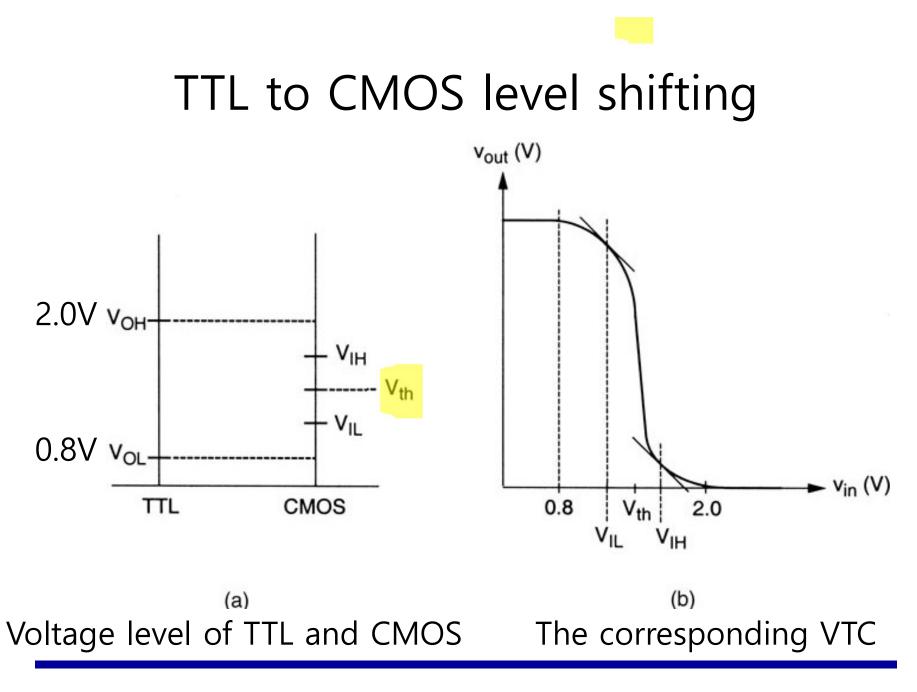

# Designing the Receiving Inverter Gate(1)

Adjust the TR ratio such that the saturation voltage at which both transistors operate in saturation region is the midpoint between 0.8V and 2.0V

Saturation voltage of the inverter gate is

$$V_{sat} = V_{th} = \frac{V_{DD} + V_{Tp} + rV_{Tn}}{1 + r}$$

$$r = \sqrt{\frac{\mu_n C_{ox} W_n / L_n}{\mu_p C_{ox} W_p / L_p}}$$

## Designing the Receiving Inverter Gate(2)

From these two equations, we get

$$\frac{W_n / L_n}{W_p / L_p} = \frac{\mu_p}{\mu_n} \left[ \frac{V_{DD} + V_{Tp} - V_{sat}}{V_{sat} - V_{Tn}} \right]^2$$

• If  $\mu_n = 3\mu_p$  and  $V_{Tn} = -V_{Tp} = 1.0V$  and  $V_{DD} = 5V$ , then in order to achieve

$$V_{sat} = \frac{0.8 + 2.0}{2} = 1.4V$$

• The nMOS-to-pMOS ratio is  $\frac{W_n / L_n}{W_p / L_p} = \frac{1}{3} \left[ \frac{5 - 1 - 1.4}{1.4 - 1} \right]^2 = \frac{169}{12}$

#### Designing the Receiving Inverter Gate(3)

$\diamond$  From the above, we get that r=6.5 and

$$V_{IL} = \frac{2V_{out} - V_{DD} + r^2 V_{Tn} + V_{Tp}}{r^2 + 1} = \frac{2V_{out} + 36.25}{43.25}$$

• where

$$V_{out}$$

satisfies the following:

$$\frac{r^2}{2}(V_{IL} - V_{Tn})^2 = (V_{DD} - V_{IL} + V_{Tp})(V_{DD} - V_{out}) - \frac{1}{2}(V_{DD} - V_{out})^2$$

• or

$$21.125(V_{IL} - 1)^2 = (4 - V_{IL})(5 - V_{out}) - \frac{1}{2}(5 - V_{out})^2$$

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

# Designing the Receiving Inverter Gate(4)

Combining these two equations,

$$21.125 \left[ \frac{2V_{out} - 7}{43.25} \right]^2 = \left[ \frac{136.75 - 2V_{out}}{43.25} \right] (5 - V_{out}) - \frac{1}{2} (5 - V_{out})^2$$

$$V_{out} = 4.97V$$

and, hence

$$V_{IL} = \frac{2 \times 4.97 + 36.25}{43.25} = 1.07V$$

Likewise,

$$V_{IH} = \frac{r^2 (2V_{out} + V_{Tn}) + V_{DD} + V_{Tp}}{r^2 + 1} = \frac{84.5V_{out} + 47.25}{43.25}$$

# Designing the Receiving Inverter Gate(5)

$\diamond$  where  $V_{out}$  satisfies the following

$$\frac{1}{2}(V_{DD} - V_{IH} + V_{Tp})^2 = r^2 \left[ (V_{IH} - V_{Tn})V_{out} - \frac{1}{2}V_{out}^2 \right]$$

$$\frac{1}{2}(4 - V_{IH})^2 = 6.5^2 \left[ (V_{IH} - 1)V_{out} - \frac{1}{2}V_{out}^2 \right]$$

Combining these two equations, we obtain

$$\frac{1}{2} \left( 4 - \frac{84.5V_{out} + 47.25}{43.25} \right)^2 = 42.25 \left[ \left( \frac{84.5V_{out} + 4}{43.25} \right) V_{out} - \frac{1}{2} V_{out}^2 \right]$$

Therefore,

$V_{out} = 0.206V$  and  $V_{IH} = 1.47V$

or

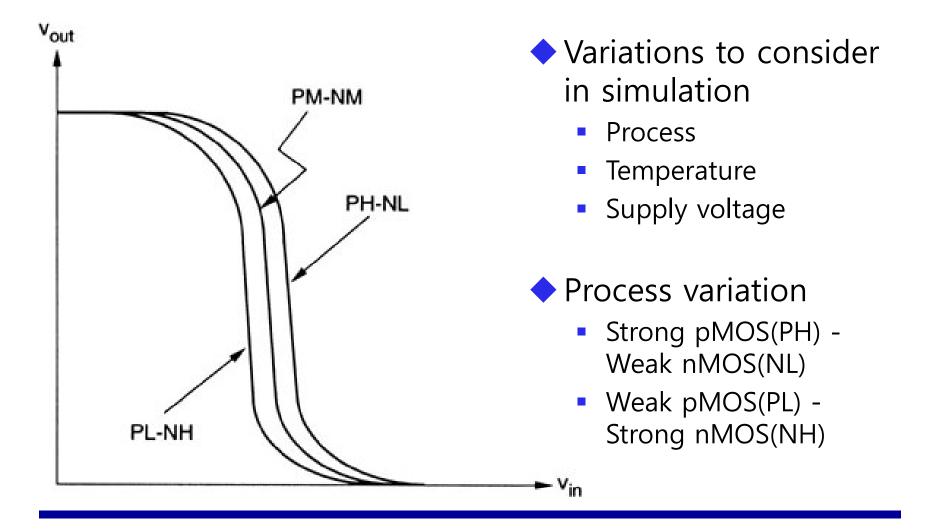

# Variation of the level-shifter VTC

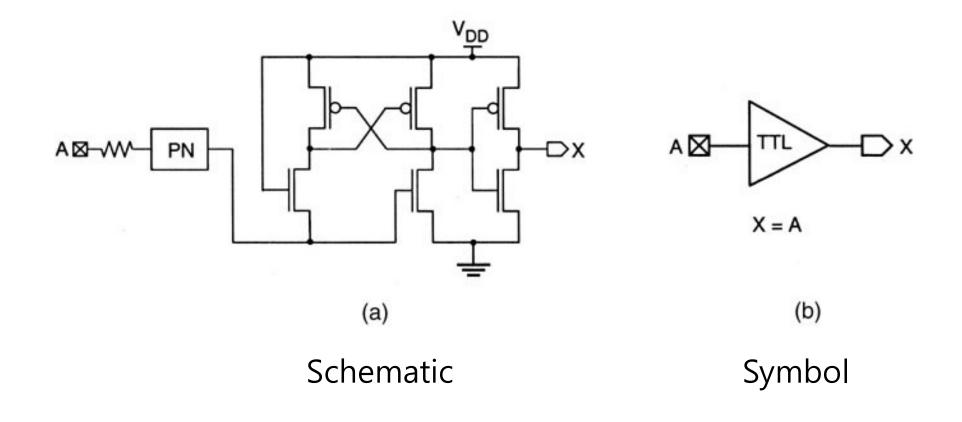

# Non-inverting TTL Level-shifting Circuit

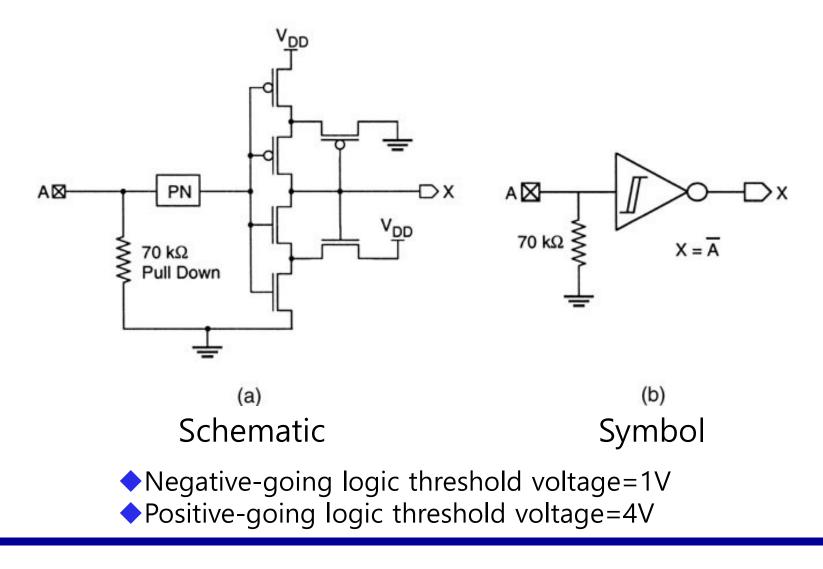

# Input Pad Circuit with Schmitt Trigger

# Tristable Output Circuit

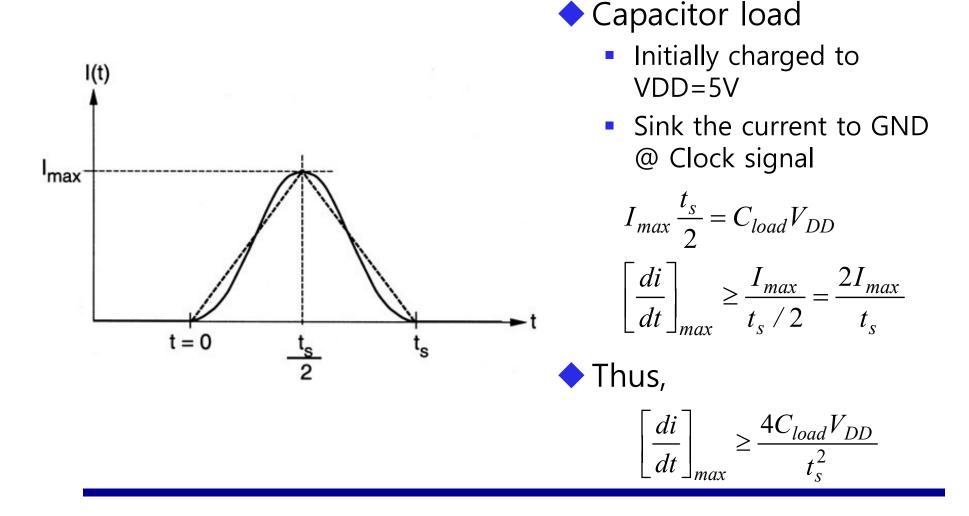

# Typical Output Circuit Current During Switching (1)

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

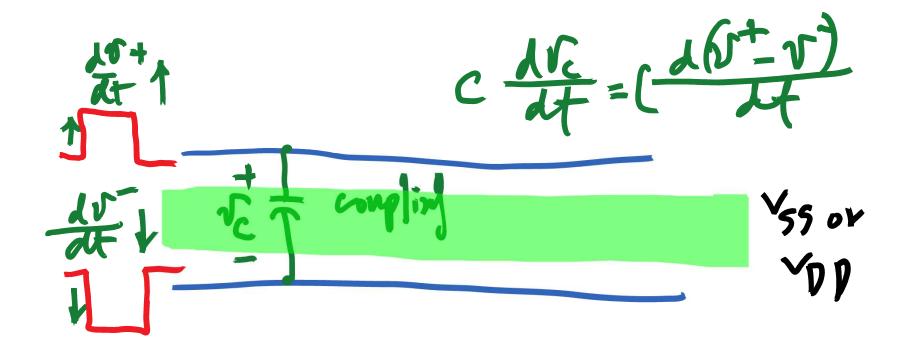

Typical Output Circuit Current During Switching (2)

• If

$$C_{load} = 100 \text{pF}$$

and  $t_s = 5 \text{ns}$ ,

$$\left[\frac{di}{dt}\right]_{\text{max}} \ge \frac{4 \times 100 \times 10^{-12} \times 5}{(5 \times 10^{-9})^2} = 80 \frac{\text{mA}}{\text{ns}}$$

And for a bonding wire with L=2, (n)

$$L\left[\frac{di}{dt}\right]_{\max} \ge 160 \text{mV}$$

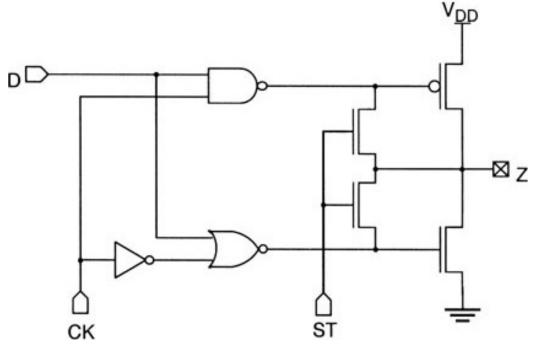

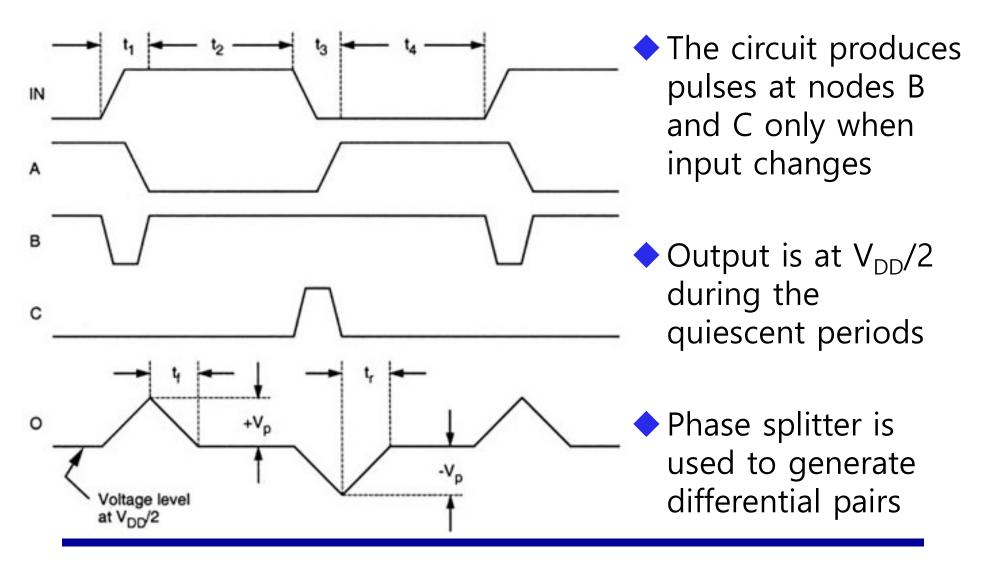

### Circuit for Reducing (*di/dt*) Noise

At strobe signal(ST), the last driver TRs are precharged

If r=1 and ST=high, the gate voltages can be precharged to VDD/2 before CK goes to high

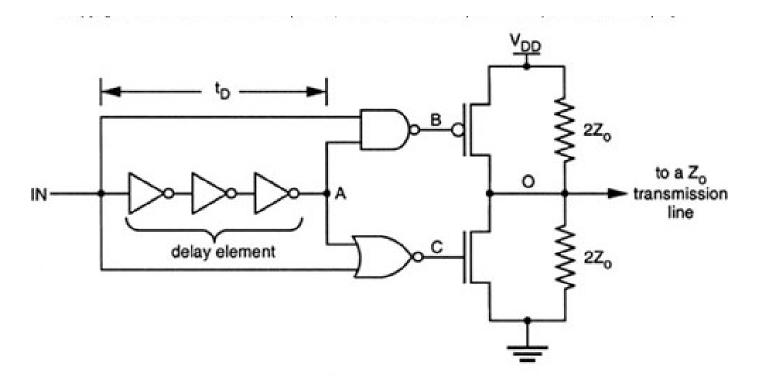

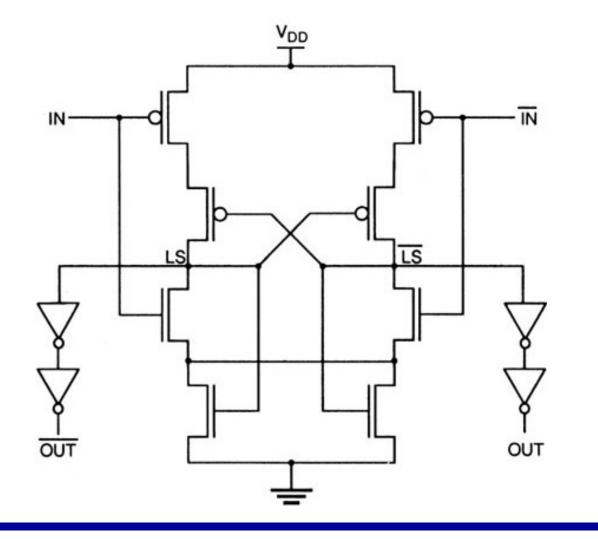

# Another Circuit for Reducing (*di/dt*) Noise

Transmits only differential signals

# Timing Diagram Of the Driver Circuit

## Receiver Circuit for Differential Data

© CMOS Pigital Integrated Circuits – 4<sup>th</sup> Edition

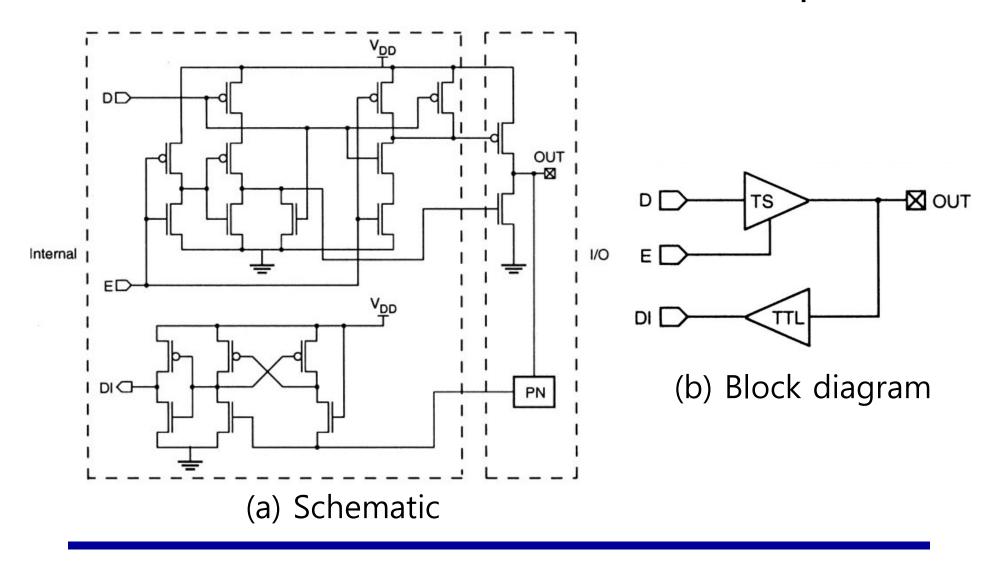

## Bidirectional Buffer with TTL Input

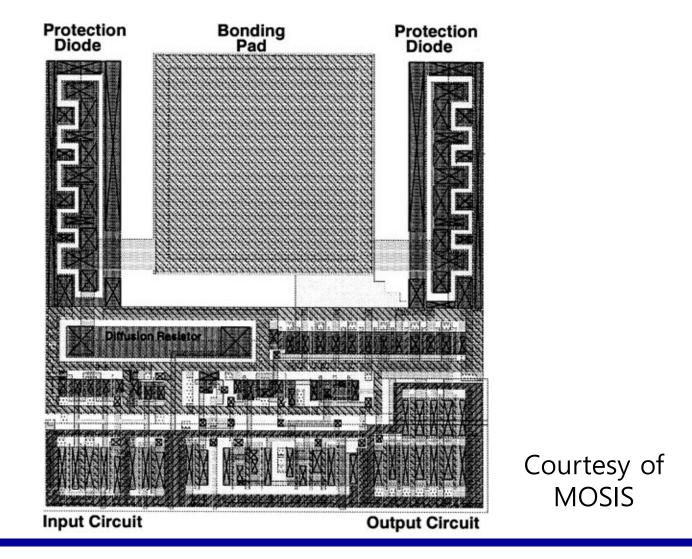

# Layout of a Bidirectional I/O Pad Circuit

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

# On-Chip Clock Generation and Distribution

#### Clock signal- heartbeats of digital systems

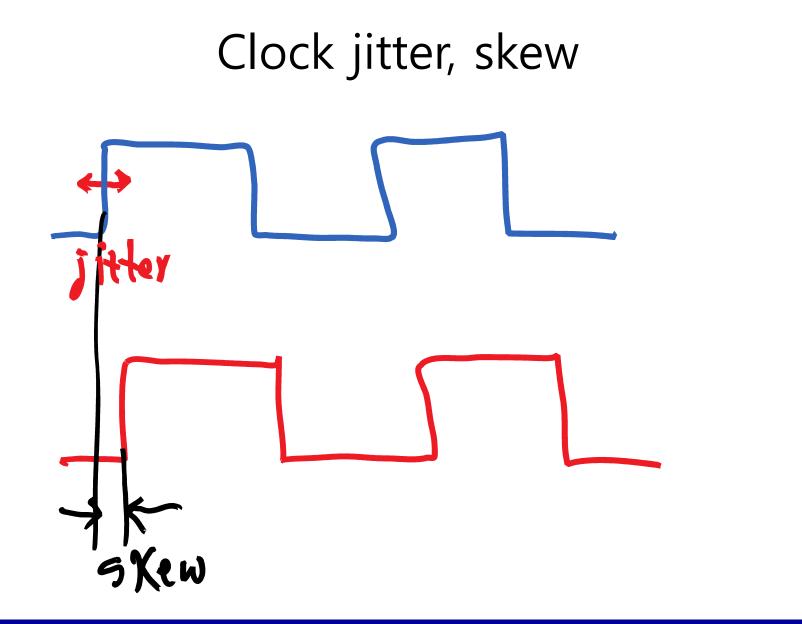

#### Skew

Spatial clock uncertainty due to PVT variations of clock buffers and interconnect lines in clock distribution network

#### ✦ Jitter

Temporal clock uncertainty from the clock generator and clock buffers

About 10% of cycle time is expended to allow realistic clock jitter and skews in computer systems

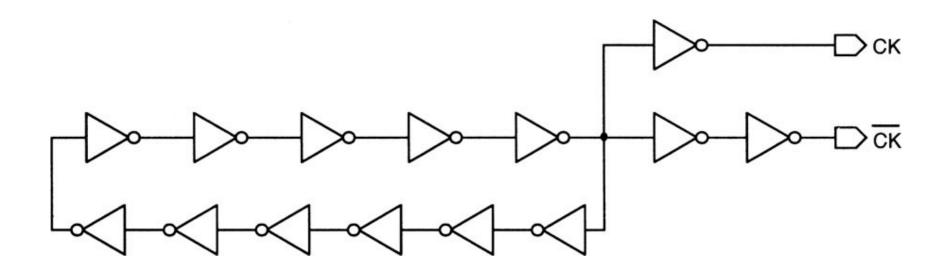

### Simple Clock Generator

- For low-end microprocessor chips

- Process-dependent

- Unstable

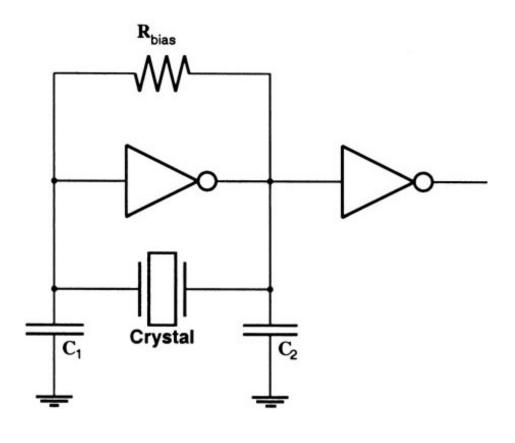

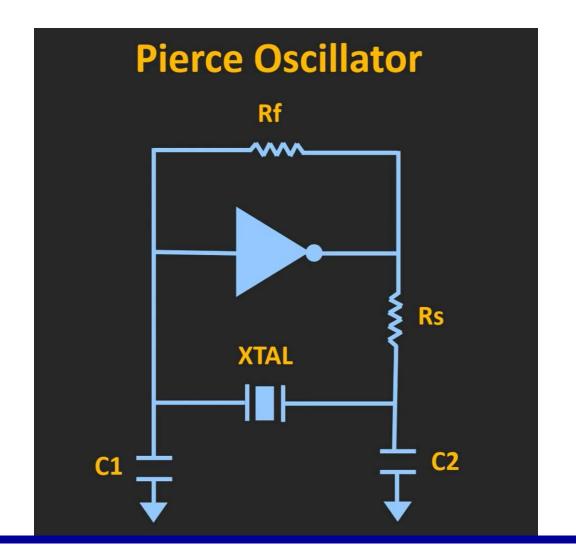

# Pierce Crystal Oscillator

- Good frequency stability

- Near series-resonant circuit

- Internal series resistance and external load

- determines the frequency and stability

- Internal inverter

- generates the voltage difference

- External inverter

- amplify the clock signal

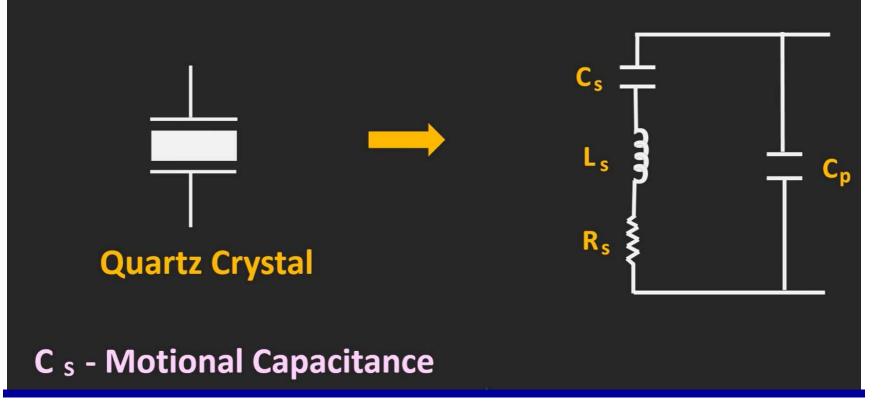

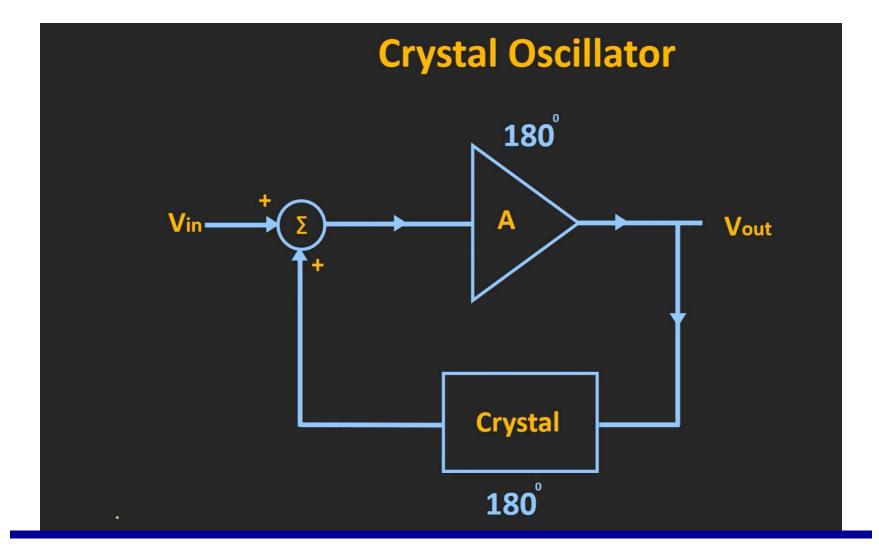

# Crystal Osc

# Feedback in Crystsal Osc.

# Osc. Frequency

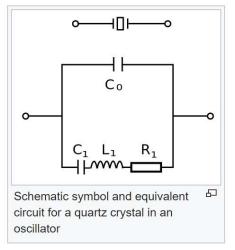

A quartz crystal can be modeled as an electrical network with a low-impedance (series) and a high-impedance (parallel) resonance points spaced closely together. Mathematically (using the Laplace transform), the impedance of this network can be written as:

$$Z(s) = \left(rac{1}{s\cdot C_1} + s\cdot L_1 + R_1

ight) \left\| \left(rac{1}{s\cdot C_0}

ight),$$

$$egin{split} Z(s) &= rac{s^2 + s rac{R_1}{L_1} + {\omega_{

m s}}^2}{(s \cdot C_0) \left[s^2 + s rac{R_1}{L_1} + {\omega_{

m p}}^2

ight]} \ &\Rightarrow \omega_{

m s} &= rac{1}{\sqrt{L_1 \cdot C_1}}, \quad \omega_{

m p} = \sqrt{rac{C_1 + C_0}{L_1 \cdot C_1 \cdot C_0}} = \omega_s \sqrt{1 + rac{C_1}{C_0}} pprox \omega_s \left(1 + rac{C_1}{2C_0}

ight) \quad (C_0 \gg C_1) \end{split}$$

where s is the complex frequency ( $s = j\omega$ ),  $\omega_s$  is the series resonant angular frequency, and  $\omega_p$  is the parallel resonant angular frequency.

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

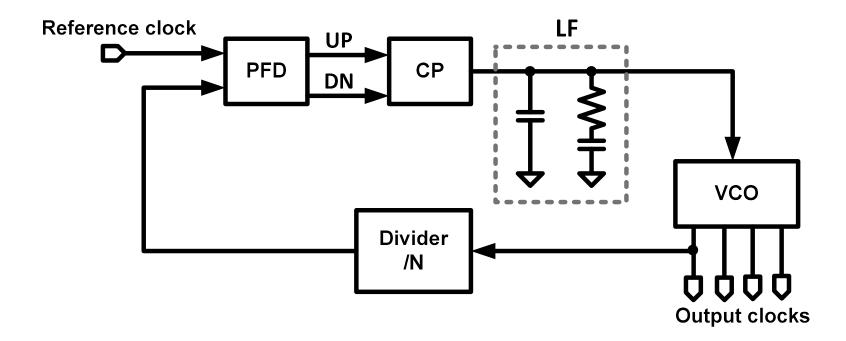

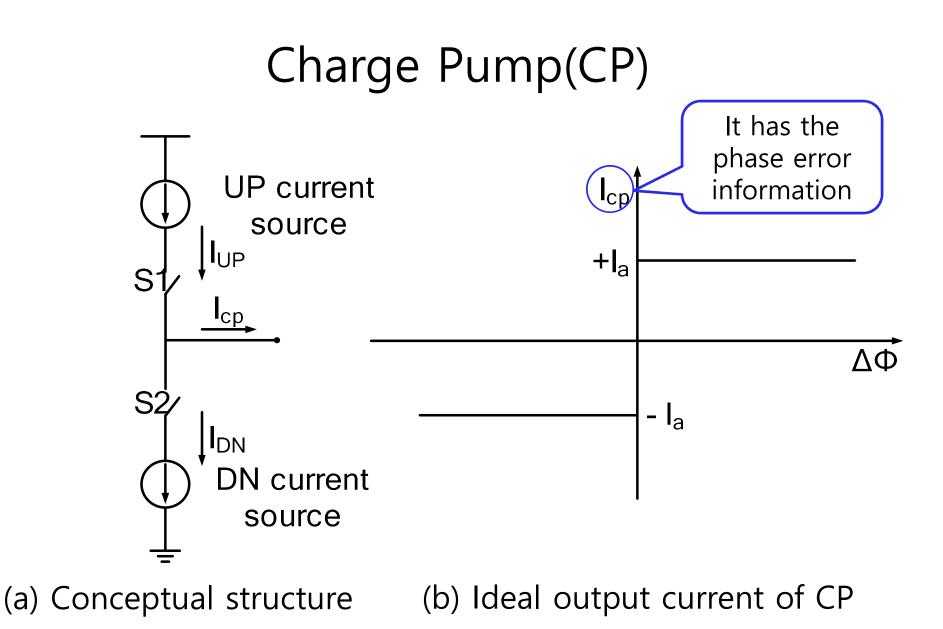

#### Phase-Locked Loop

The most common on-chip clock generator

Easy multiplication of frequency

• Frequency of VCO : N times as faster as the reference clock

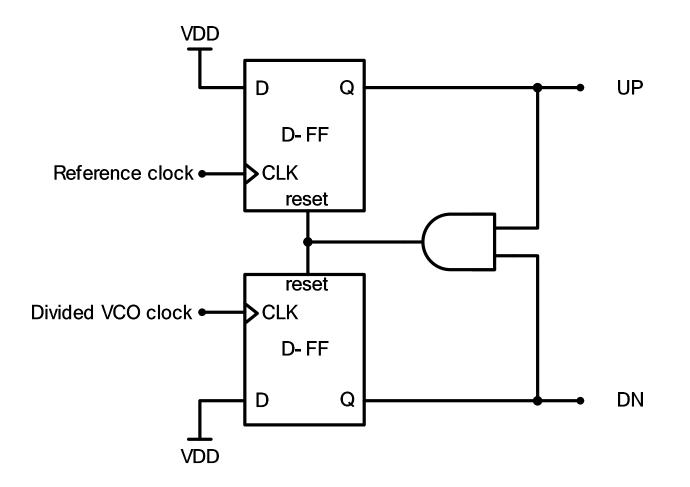

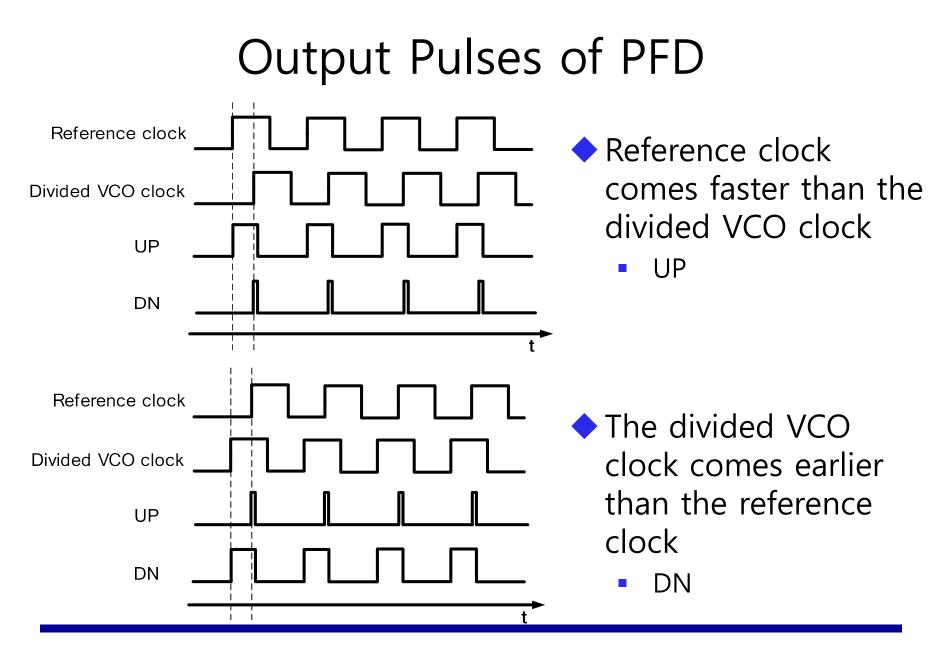

### Phase Frequency Detector(PFD)

### Locked state of PLL

- Locked state of PLL

- Two clocks come very close

- Dead zone problem

- If the phase difference of two PFD inputs is as small as few pico seconds, the PFD cannot generate a proper pulse

- because it takes time for the PFD circuit to respond to the input signals

- In this case, the pulse width of PFD output would be too small to represent the exact amount of phase error

- It can be solved by inserting a buffer at the reset path to add some delay

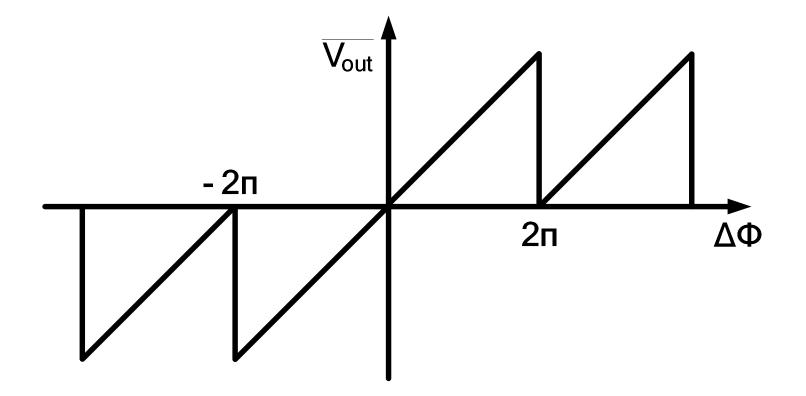

## Input and Output Characteristic of PFD

# Oscillator

Oscillator - unstable system that generates repetitive signals

- Oscillation conditions

- Loop gain > 1

- Total phase shift = 360

- Barkhausen criterion

- Loop gain, phase shift:  $|H(j\varpi_0)| \ge 1$ ,  $\angle H(j\varpi_0) = 180^\circ$

- Simple and intuitive

- Bode plot

- Necessary but not sufficient to stability

- Nyquist stability criterion

- Accurate

- Root-locus plot

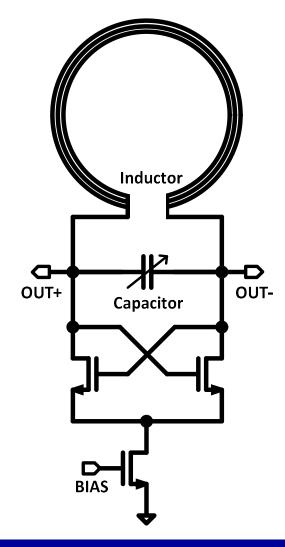

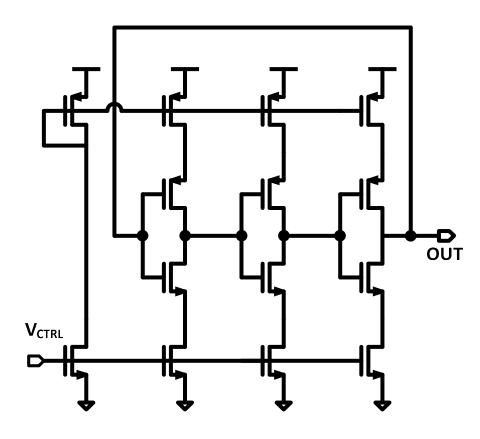

## Voltage Controlled Oscillator(VCO)

#### VCO

- Oscillator whose frequency is controlled by the voltage

- Noise budget of the VCO

- determines the jitter performance and loop bandwidth of PLL

$$\omega_{out} = \omega_0 + \int K_{VCO} V_{CTRL} dt$$

- $\omega_{out}$  : output frequency

- $\omega_0$  : initial VCO frequency

- K<sub>VCO</sub> : VCO gain

- V<sub>CTRL</sub> : VCO control voltage

## Factors to Consider in VCO (1)

#### Free running frequency

VCO operating frequency in the absence of control voltage

#### Tuning range

- The range of frequency that VCO can generate

- It determines the operating range of PLL

- Noise rejection ability

- A measure of how much noise from external environment the VCO can filter out

- Supply noise rejection / Common-mode noise rejection

### Factors to Consider in VCO (2)

#### Power consumption

- Critical to low-power applications

- The more power, the better jitter performance

#### Output signal purity

- The most important factor

- Clock jitter / phase noise

### Harmonic Oscillator

- Resonance of the energy components such as LCtank

- Good signal purity

- But bulky (inductor and capacitor)

- Tuning range narrow

- Not suitable for digital systems

#### **Relaxation Oscillator**

- Chain of delay elements

- Easy to design

- Compact size

- Bad signal purity

- Typical example: ring oscillator

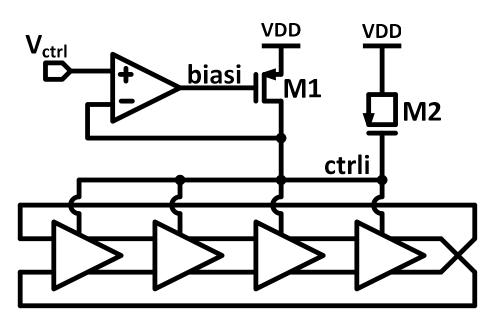

## VCO with Supply Noise Rejection

- Regulated voltage ctrli

- robust to supply noise

- Opamp BW > PLL BW

- 🔶 M1: large

- Enough voltage headroom

- Wide operating range of VCO

- M2: suppress ripples on ctrli

- Dominant pole on node ctrli

- Compensation capacitor and resistor are needed between node biasi and ctrli

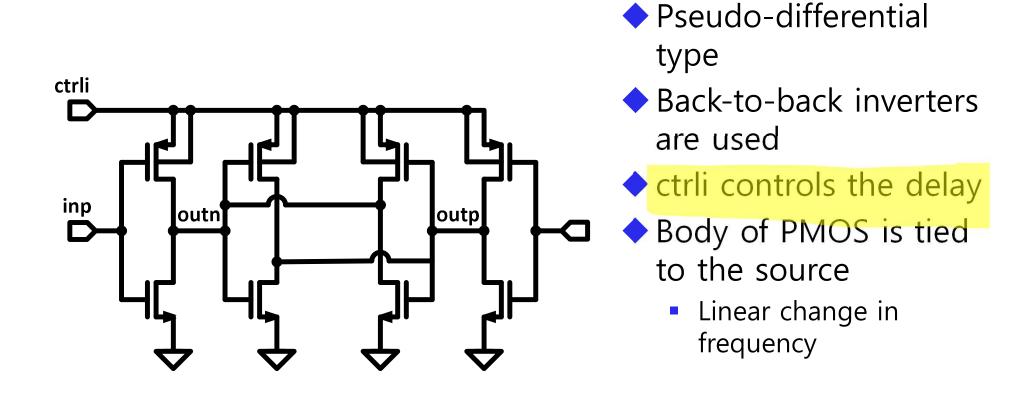

### Delay Cell

Additional resistor introduces zero for larger phase margin

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

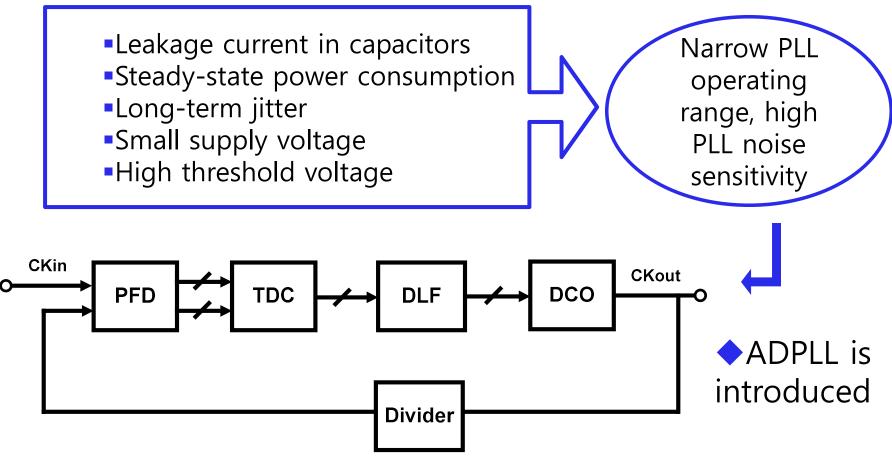

## All-Digital PLL(ADPLL)

Issues in analog PLL in deep-submicron process

## Components of ADPLL

#### Phase-Frequency Detector(PFD)

Time-to-digital converter(TDC)

- converts phase difference to digital words

- replaces CP

- Digital loop filter(DLF)

- filters out digital input words

- Digitally controlled oscillator(DCO)

- replaces a VCO

## Advantage/Disadvantage of ADPLL

#### 🔶 Advantage

- Excellent timing accuracy

- No analog circuits that suffer from small voltage headroom and relatively high threshold voltage

- Robust to PVT variation

- Only TDC and DCO are sensitive

- Good for deep-submicron processes

#### Disadvantage

- Limited resolution in phase detection by TDC

- Small resolution in frequency control by DCO

- Possibly more jitter than analog PLL

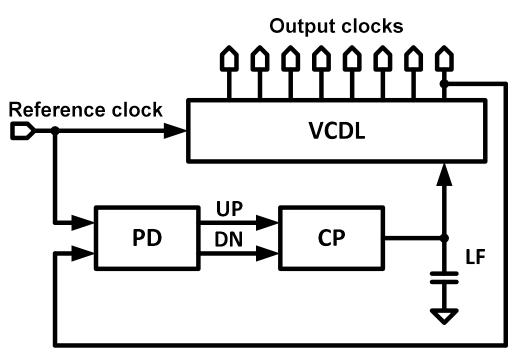

# Delay-Locked Loop(DLL)

- VCDL adjusts the delay by a control voltage

- DLL adjusts the phase of VCDL / PLL modifies the frequency

- PLL has one more pole than DLL (2<sup>nd</sup>-order)

- No stability issue in DLL

## Simulation of DLL Locking Process

## Comparison of PLL and DLL

| PLL                                                          | DLL                                                                                      |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------|

| VCO-Jitter accumulation                                      | VCDL–No jitter accumulation                                                              |

| Higher-order system<br>- Can be unstable<br>- Hard to design | 1 <sup>st</sup> -order system<br>- Always stable<br>- Easier to design                   |

| Costly to integrate LF                                       | Easier to integrate LF                                                                   |

| Less Ref. signal dependent                                   | Ref. signal dependent                                                                    |

| Easy Freq. multiplication                                    | Difficult Freq. multiplication                                                           |

| No limited locking range                                     | Limited locking range<br>T <sub>Ref</sub> < VCDL <sub>delay</sub> < 3T <sub>Ref</sub> /2 |

| EMI problem                                                  | Less EMI Problem                                                                         |

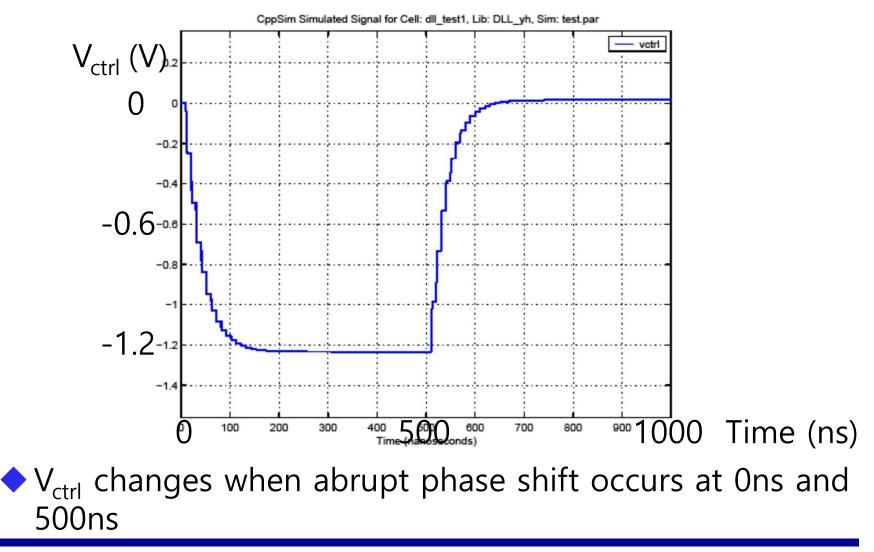

### Non-overlapping Clock Generator

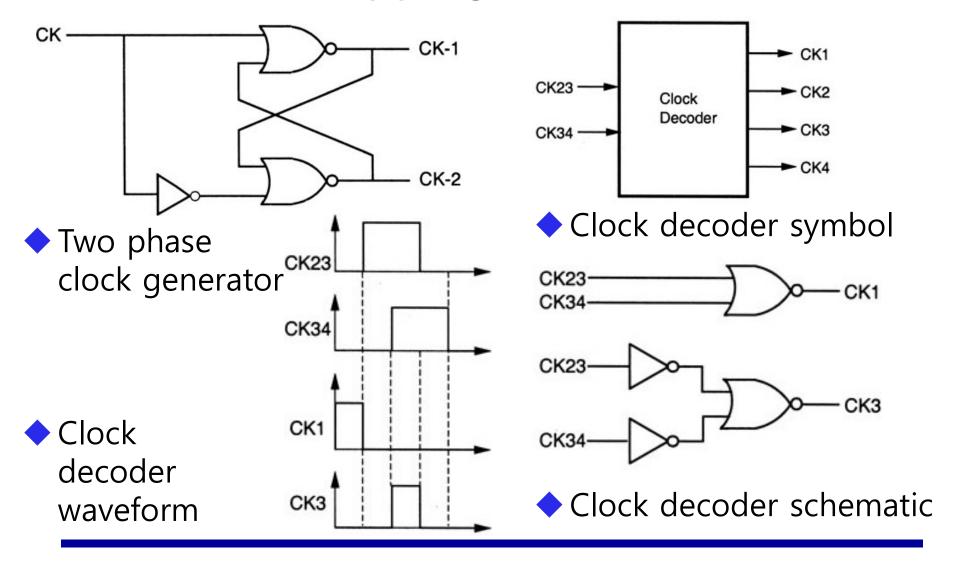

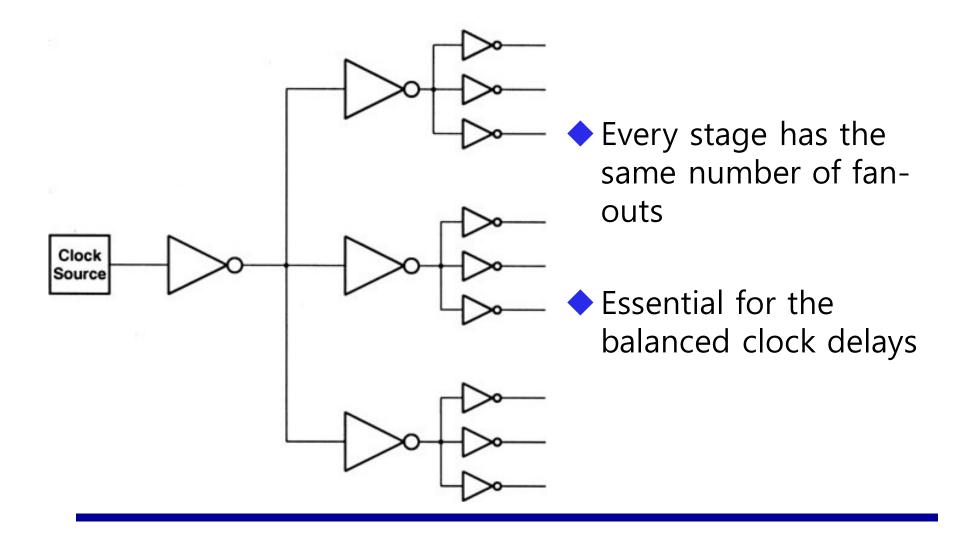

#### Uniform Clock Distribution(H-tree)

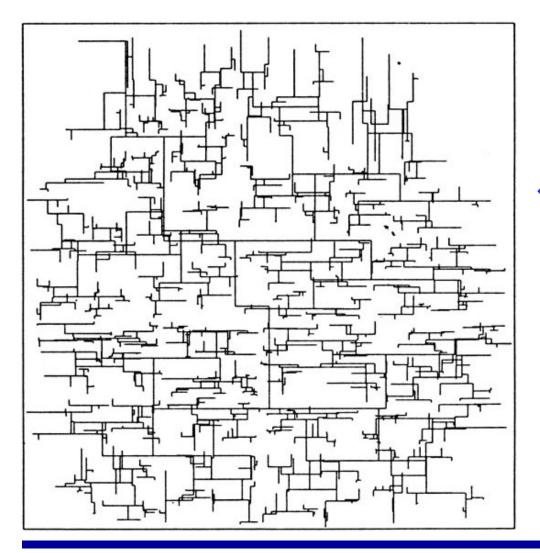

#### Zero-Skew Network By CAD

An example of the zero-skew clock routing network, generated by a computer-aided design(CAD) tool

#### **Buffered Clock Distribution Network**

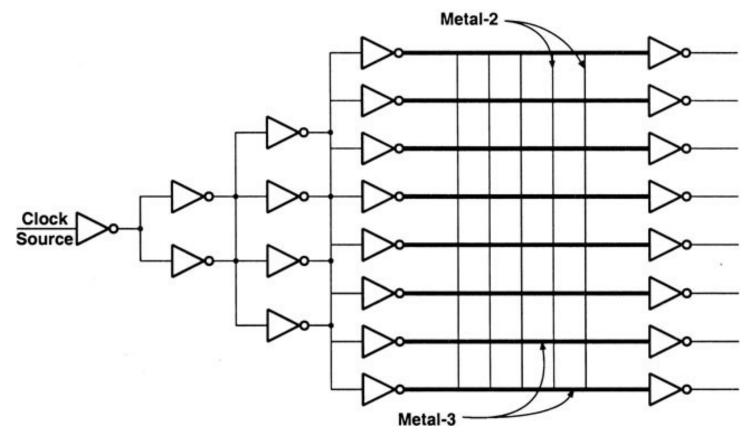

## Clock Distribution in the DEC Alpha Chip

Mesh pattern of interconnect wires

Clock signals are kept in phase across the entire chip

## Considerations For VLSI Design

- $\diamond$  Ideal duty cycle of a clock = 50%

- Feedback based on the voltage average improves the duty

- t<sub>r</sub> and t<sub>f</sub> should not be reduced excessively for prevention of reflection in the interconnection network

- Small load cap reduces the fan-out, the interconnect lengths, and the gate capacitances

- Small impedance of clock line by increasing the (w/h) ratios (the ratio of the line width to vertical separation distance of the line from the substrate)

- Cross-talk prevention

- Adequate separation between clock lines

- Power or ground rail between high-speed lines

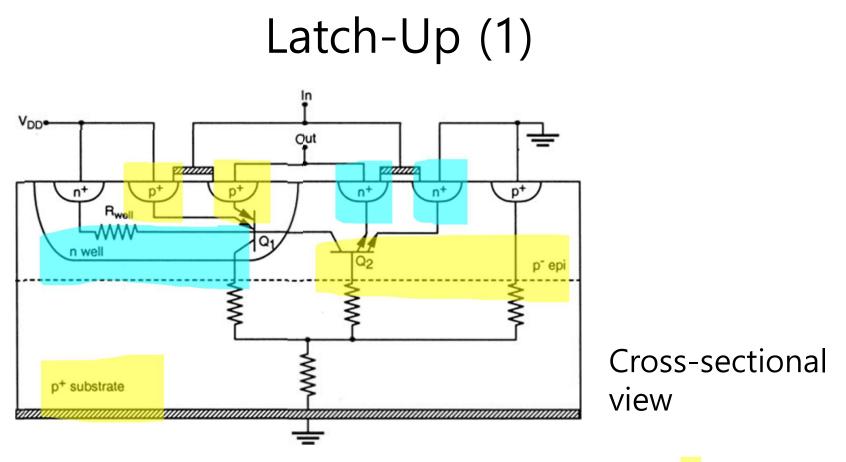

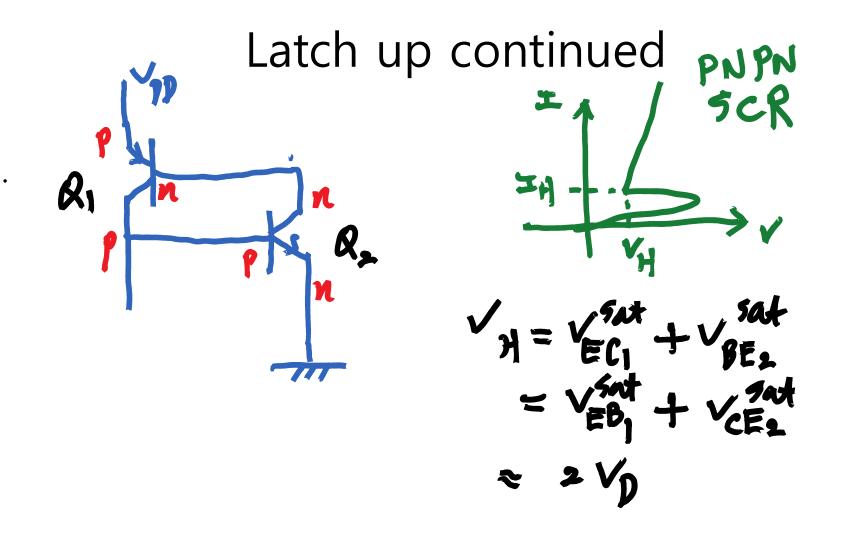

Silicon-controlled rectifier(SCR) with positive feedback

- Excessive current flow -> device damage

- Concerns of esp. I/O circuits

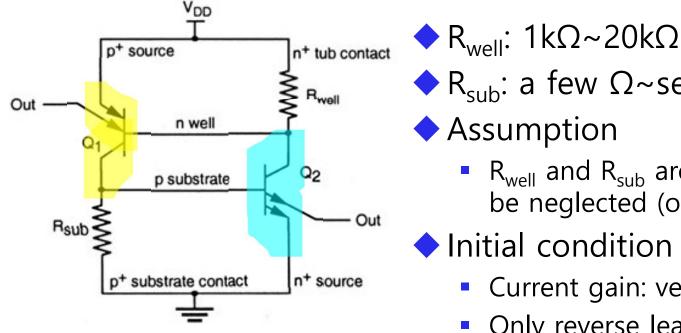

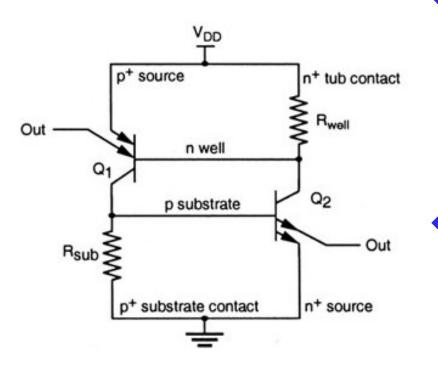

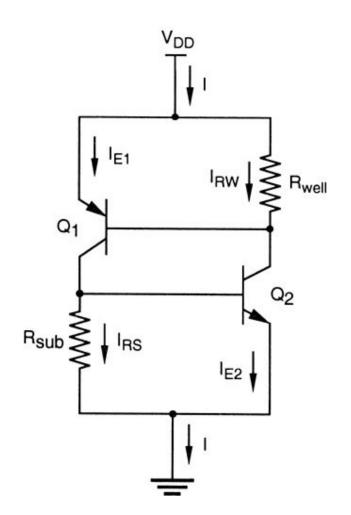

#### Circuit Model of Latch-Up

$\mathbf{R}_{sub}$ : a few Ω~several hundred Ω Assumption

- R<sub>well</sub> and R<sub>sub</sub> are large enough to be neglected (open circuit)

- Initial condition

- Current gain: very low

- Only reverse leakage currents flows

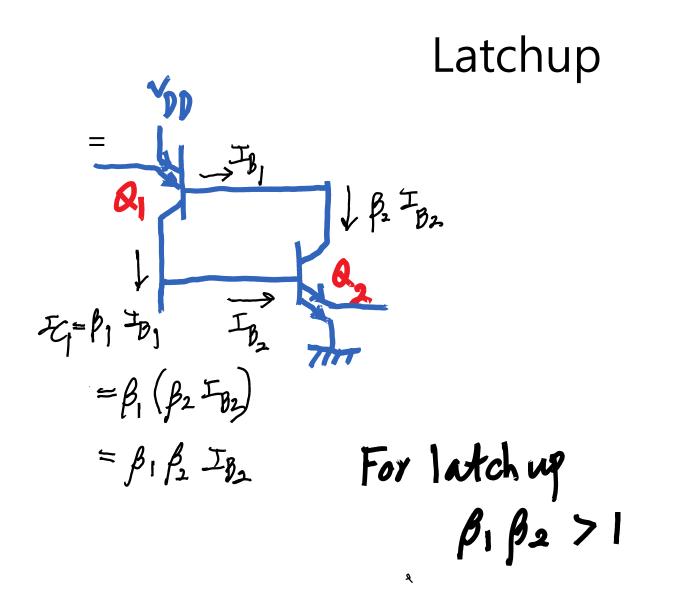

## Triggering the Latch-Up

Trigger process

- I<sub>C</sub> of one of BJTs is increased by an external disturbance

- Feedback loop multiplies it by (β1· β2) -> positive feedback

- Low-impedance path is formed

- Trigger condition

$\beta_1 \cdot \beta_2 \ge 1$

Or

$$\frac{\alpha_1}{1-\alpha_1} \cdot \frac{\alpha_2}{1-\alpha_2} \ge 1 \quad \Rightarrow \quad \alpha_1 + \alpha_2 \ge 1$$

$$\frac{1}{2} \cdot pT_{B}$$

$$\frac{1}{2} \cdot pT_{B}$$

$$\frac{1}{2} \cdot qT_{E}$$

$$\frac{1}{2} \cdot q$$

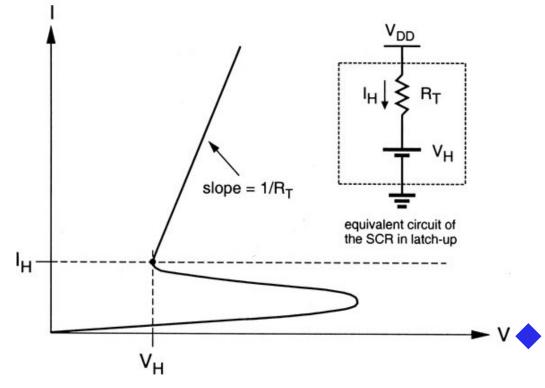

### Current-Voltage Characteristics of a SCR

Voltage drop across the SCR in latch-up

> $V_H = V_{BE1,sat} + V_{CE2,sat}$ =  $V_{BE2,sat} + V_{CE1,sat}$

- V<sub>H</sub> : holding voltage

- I<sub>H</sub> : holding current

- Low impedance state if  $I > I_H$

R<sub>T</sub> : total parasitic R in the current path

## Causes for Latch-Up

#### Large slew rate of VDD during initial start-up

- Displacement currents

- By well junction capacitance in the substrate and the well

- *Dynamic recovery* if the slew rate is not very high

- I/O signal swing much over VDD or far below VSS

- By impedance mismatches in transmission lines

- ESD stress

- Minority carrier injection: clamping device → substrate or well

- Sudden transients in buses

- Due to simultaneous switching of many drivers

- Leakage currents in well junctions

Radiation of X-rays, cosmic rays, or alpha particles

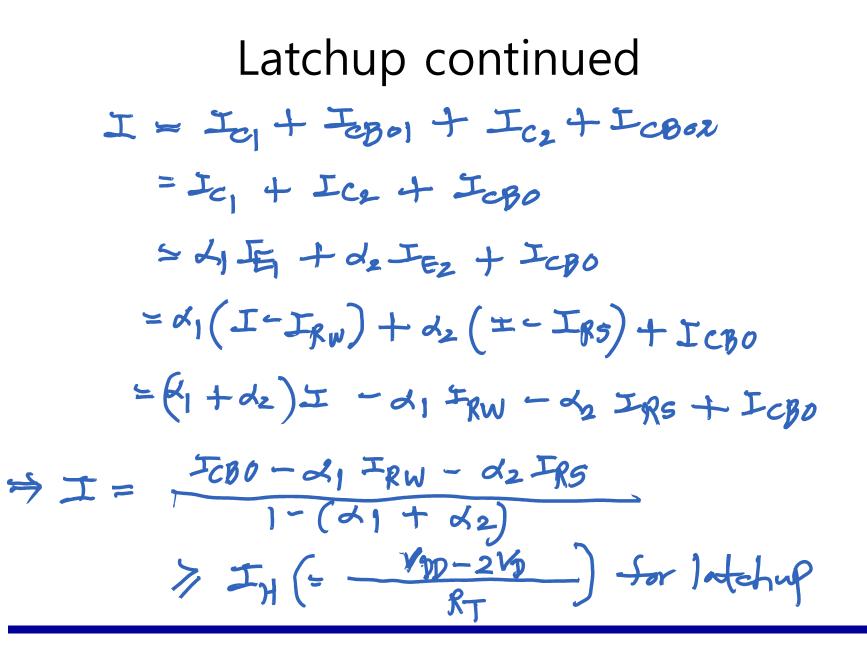

# Derivation of $I_{H}(1)$

◆ From left figure, I = I<sub>E1</sub> + I<sub>RW</sub> I = I<sub>E2</sub> + I<sub>RS</sub>

◆ From relations of Q1 and Q2, I<sub>C1</sub> = α<sub>1</sub>I<sub>E1</sub> = α<sub>1</sub><sup>0</sup>I I<sub>C2</sub> = α<sub>2</sub>I<sub>E2</sub> = α<sub>2</sub><sup>0</sup>I

◆ α<sub>1</sub><sup>0</sup>, α<sub>2</sub><sup>0</sup> : equivalent collector-to-emitter current gains absorbing the

effects of parasitic R into TRs

The SCR current I,

$$I = I_{C1} + I_{C2} + (I_{CBO1} + I_{CBO2})$$

### Derivation of $I_{H}$ (2)

From above equations,

$$I = \frac{I_{CBO} - (I_{RS}\alpha_{1} + I_{RW}\alpha_{2})}{1 - (\alpha_{1} + \alpha_{2})}$$

$\bullet$  *I<sub>H</sub>* is defined as the current with zero *I<sub>CBO</sub>*

$$I_H = \frac{I_{RS}\alpha_1 + I_{RW}\alpha_2}{\alpha_1 + \alpha_2 - 1}$$

• If  $\alpha_1 + \alpha_2$  is close to 1,  $I_H$  will be large • The SCR current at the onset of latch-up,

$$I \ge I_H = (V_{DD} - V_H) / R_T$$

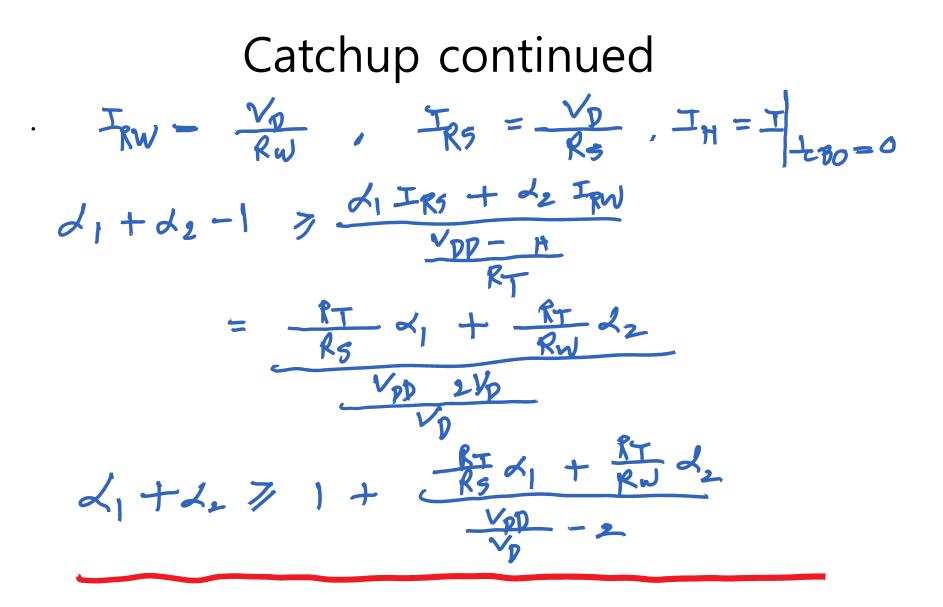

#### Latch-Up Condition

Both transistors are at the saturation boundary

$$V_{H} = 2V_{BE} \text{ with } V_{BE1} = V_{BE2} = V_{BE}$$

$$I_{RW} = V_{BE} / R_{well} \text{ and } I_{RS} = V_{RE} / R_{sub}$$

Therefore, the condition for latch-up is

$$\alpha_1 + \alpha_2 \ge 1 + \left(\frac{\frac{R_T}{R_{well}}\alpha_1 + \frac{R_T}{R_{sub}}\alpha_2}{\frac{V_{DD}}{V_{BE}} - 2}\right)$$

Above inequality shows that small R<sub>sub</sub> and R<sub>well</sub> help avoiding the latch-up

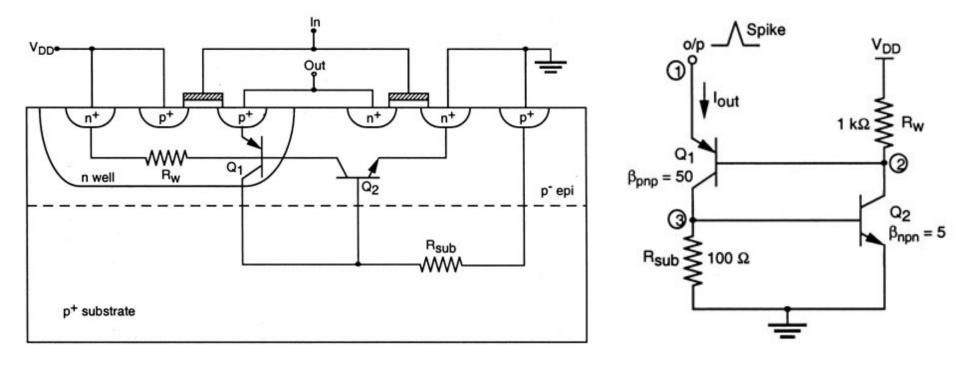

#### Simulation of Latch-Up (Schematic)

(a) CMOS inverter with parasitic BJTs

(b) Schematic of the simulation

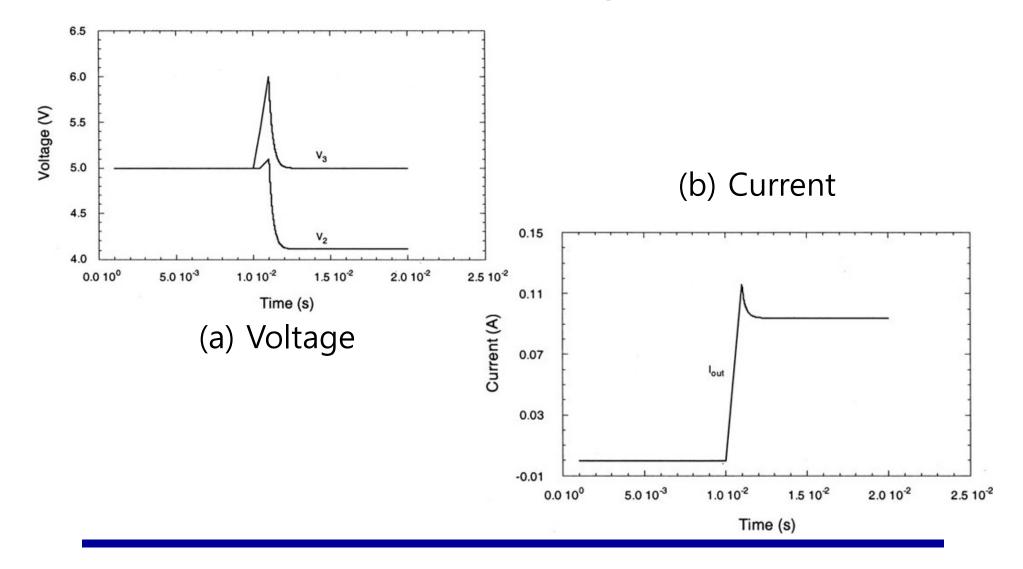

#### Simulation of Latch-Up (Waveform)

© CMOS Digital Integrated Circuits – 4<sup>th</sup> Edition

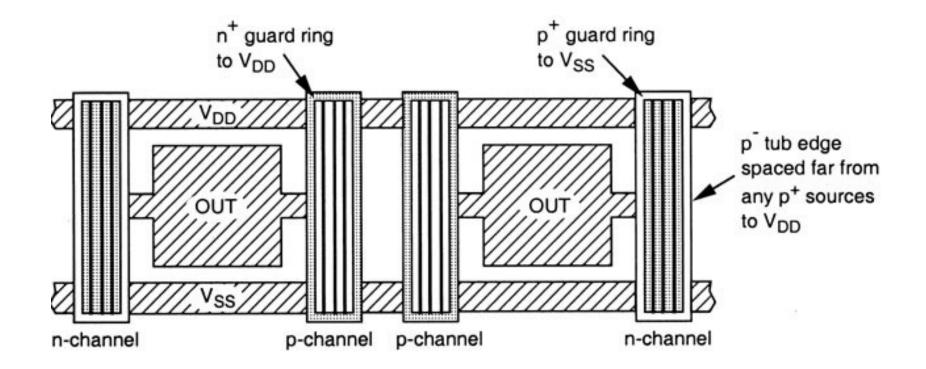

# Latch-Up Guidelines(1)

- Gold doping of the substrate

- Reduce gains of BJTs by lowering the minority carrier lifetime

- Schottky source/drain contacts

- Reduce the minority carrier injection efficiency of BJT emitters

- Guardband rings: capture the injected minority carriers

- P+ guard rings connected to ground around nMOS

- N+ guard rings connected to V<sub>DD</sub> around pMOS

- Place substrate and well contacts as close as possible to the source of MOS transistors

- Reduce R<sub>w</sub> and R<sub>sub</sub>

- Minimum area p-wells (in case of twin-tub technology or n-type substrate)

# Latch-Up Guidelines(2)

- Source diffusion regions of pMOS transistors should be placed.

- Ensure the same potential between V<sub>DD</sub> and p-wells

- In some n-well I/O circuits, wells can be eliminated by using only nMOS

- Avoid the forward biasing of source/drain junctions

- Prevents injecting high current

- Lightly doped epitaxial layer on top of a heavily doped substrate

- Shunts lateral currents from the vertical transistor

- $\blacklozenge$  Place nMOS close to V<sub>SS</sub> and pMOS near V<sub>DD</sub>

Maintain sufficient space between pMOS and nMOS

# I/O Cell Layout With Latch-Up Guidelines